全数字锁相环的verilog源代码

2013-03-28

15

仿真已通过 module dpll(reset,clk,signal_in,signal_out,syn); parameter para_K=4; parameter para_N=16; input reset; input clk; input signal_in; output signal_out; output syn; reg signal_out; reg dpout; reg delclk; reg addclk; reg add_del_clkout; reg [7:0]up_down_cnt; reg [2:0]cnt8; reg [8:0]cnt_N; reg syn; reg ..

[查看全文]

用FPGA设计一阶全数字锁相环

2013-02-15

22

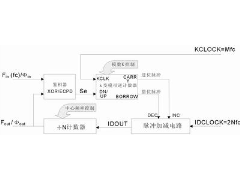

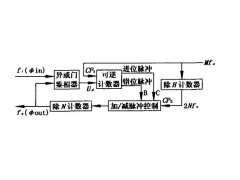

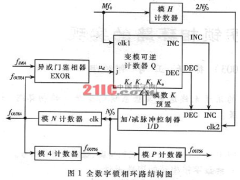

摘要:本文在说明全数字锁相环的基础上,提出了一种利用FPGA设计一阶全数字锁相环的方法,并给出了关键部件的RTL可综合代码,并结合本设计的一些仿真波形详细描述了数字锁相环的工作过程,最后对一些有关的问题进行了讨论。 引言 锁相环(PLL)技术在众多领域得到了广泛的应用。如信号处理,调制解调,时钟同步,倍频,频率综 ..

[查看全文]

基于VHDL 的全数字锁相环的设计

2012-12-29

倪虹霞 杨信昌

19

摘要:叙述了全数字锁相环的工作原理,提出了应用VHDL 技术设计全数字锁相环的方法,并用复杂可编程逻辑器件CPLD 予以实现,给出了系统主要模块的设计过程和仿真结果。 0引言 全数字锁相环(DPLL) 由于避免了模拟锁相环存在的温度漂移和易受电压变化影响等缺点。从而具备可靠性高、工作稳定、调节方便等优点。在调制解调、频率合 ..

[查看全文]

CD4046锁相环原理及应用

2012-11-21

47

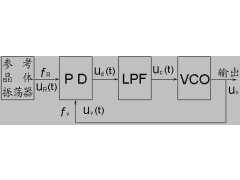

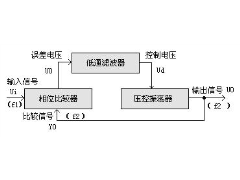

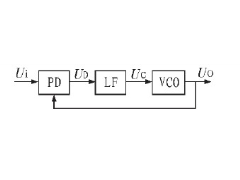

锁相的意义是相位同步的自动控制,能够完成两个电信号相位同步的自动控制闭环系统叫做锁相环,简称PLL。它广泛应用于广播通信、频率合成、自动控制及时钟同步等技术领域。锁相环主要由相位比较器(PC)、压控振荡器(VCO)、低通滤波器三部分组成,如图1所示。 图 1压控振荡器的输出Uo接至相位比较器的一个输入端,其输出 ..

[查看全文]

FPGA 可编程全数字锁相环路的实现

2012-10-22

12

锁相环路已在模拟和数字通信及无线电电子学等各个领域中得到了极为广泛的应用,特别是在数字通信的调制解调和位同步中常常要用到各种各样的锁相环。锁相就是利用输入信号与输出信号之间的相位误差自动调节输出相位使之与输入相位一致,或保持一个很小的相位差。最初的锁相环全部由模拟电路组成,随着大规模、超高速数字集成 ..

[查看全文]

基于锁相环的低频函数发生器

2012-10-03

70

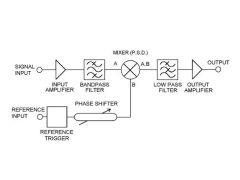

摘要:介绍了锁相环的原理以及Freescale 公司的锁相环频率合成器件MC145151- 2 的主要特点,给出了MC145151- 2 和ICL8038 低频锁相环函数发生器的工作原理、设计思想、电路结构、模块设计方法及其电路原理图。 1、引言 电子系统中经常需要采用频率和幅度可调的正弦波信号作为基准或载波信号。而正弦波信号主要是由模拟电路 ..

[查看全文]

以4046锁相环为核心构成的超声波接收器电路

2012-09-30

40

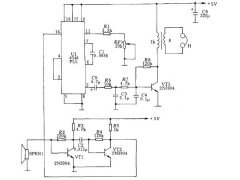

图中所示话筒SPKR1接收频率为20kHZ的超声波信号,经由压控振荡器调谐到19kHz上,此信引加到锁相环(PLL)集成电路4046输入端。由引脚2输出差颇为1kHz的信号,再经过晶体管VT3放大和变压器耦台,最后由耳机收到可听见的声音。如果接收信号频率增加到22kHz,则住耳机内能听到3kHz的单音声音。按图中给出的C1、Rl和R9的数 ..

[查看全文]

锁相环CD4046应用介绍

2012-09-27

33

锁相的意义是相位同步的自动控制,能够完成两个电信号相位同步的自动控制闭环系统叫做锁相环,简称PLL。它广泛应用于广播通信、频率合成、自动控制及时钟同步等技术领域。锁相环主要由相位比较器(PC)、压控振荡器(VCO)。低通滤波器三部分组成,如图1所示。 图1 压控振荡器的输出Uo接至相位比较器的一个输入端,其输出 ..

[查看全文]

CD4046锁相环原理及应用

2012-09-09

54

锁相的意义是相位同步的自动控制,能够完成两个电信号相位同步的自动控制闭环系统叫做锁相环,简称PLL。它广泛应用于广播通信、频率合成、自动控制及时钟同步等技术领域。锁相环主要由相位比较器(PC)、压控振荡器(VCO)、低通滤波器三部分组成,如图1所示。 图 1 压控振荡器的输出Uo接至相位比较器的一个输入端,其输出 ..

[查看全文]

推荐文章

最新文章

热门文章