protel99se信号完整性应用

2013-04-03

27

本文由于时间关系,只说明了操作步骤,应用者需要具备对protel99se比较深的操作能力和信号完整性理论基础以及对现代EDA软件的约束驱动设计方法有一定的了解。至于自己为什么会考虑protel99se来做信号完整性分析,是因为公司的原因,公司本来想上cadence,但自从我来到就职公司后,凭经验做的板子还都过得去,目前还没有什 ..

[查看全文]

利用Cadence Allegro进行PCB级的信号完整性仿真

2013-02-28

李新 张琳

21

摘要:在高速PCB设计过程中仅仅依靠个人经验布线,往往存在巨大的局限性.利用Cadence的Allegro软件包对电路进行PCB级的仿真,可以最优化线路布局,极大地提高电路设计质量,从而缩短设计周期,本文结合作者的实际设计经验.介绍使用Cadence的一般步骤并列举在使用过程中所发现的一些问题. 随着信息宽带化和高速化的发展,以前的低 ..

[查看全文]

高速电子线路的信号完整性设计(一)

2012-11-16

于波

24

1、引言 当今电子技术的发展日新月异,大规模超大规模集成电路越来越多地应用到通用系统中。同时,深亚微米工艺在IC设计中的使用,使得芯片的集成规模更大。从电子行业的发展来看,1992年只有40%的电子系统工作在30MHz以上的频率,而且器件多数使用DIP、PLCC等体积大、管脚少的封装形式,到1994年已有50%的设计达到了5 ..

[查看全文]

高速电路设计中信号完整性分析

2012-09-06

华文龙

46

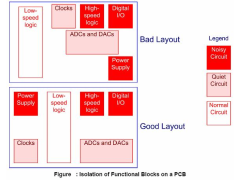

由于系统时钟频率和上升时间的增长,信号完整性设计变得越来越重要。不幸的是,绝大多数数字电路设计者并没意识到信号完整性问题的重要性,或者是直到设计的最后阶段才初步认识到。本篇介绍了高速数字硬件电路设计中信号完整性在通常设计的影响。这包括特征阻抗控制、终端匹配、电源和地平面、信号布线和串扰等问题。掌握这 ..

[查看全文]

信号完整性的一些基本概念

2012-08-03

55

信号完整性(Signal Integrity):就是指电路系统中信号的质量,如果在要求的时间内,信号能不失真地从源端传送到接收端,我们就称该信号是完整的。 传输线(Transmission Line):由两个具有一定长度的导体组成回路的连接线,我们称之为传输线,有时也被称为延迟线。 集总电路(Lumped circuit):在一般的电路分析中,电路的 ..

[查看全文]

电地完整性、信号完整性分析导论

2012-07-22

36

14.1.简介在高速数字设计的领域里,信号完整性已经变成了一个关键的问题,给设计工程师带来了越来越严峻的考验。许多信号完整性问题本质上来说是电磁现象,和本书前面章节中讨论的EMI/EMC 部分相关。本章我们将要讨论典型的信号完整性问题及其成因,为什么我们要理解它们以及我们如何来分析和解决这些问题。同时介绍几个目 ..

[查看全文]

高速电子线路的信号完整性设计(三)

2012-06-29

于波

19

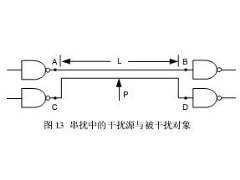

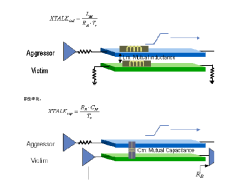

5、串扰分析 当今飞速发展的电子设计领域,高速化和小型化已经成为一种趋势。如何在缩小电子系统体积的同时,保持并提高系统的速度与性能成为摆在设计者面前的一个重要课题。信号频率变高,边沿变陡,印刷电路板的尺寸变小,布线密度加大等都使得串扰越来越成为一个值得注意的问题。而随着电子工程师不断把设计推向技术与工艺 ..

[查看全文]

高速电子线路的信号完整性设计(二)

2012-06-02

于波

13

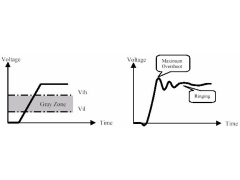

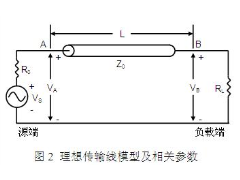

4、信号发射与端接技术 4.1、 信号反射的形成 传输线上的阻抗不连续会导致信号反射,我们以图2所示的理想传输线模型来分析与信号反射有关的重要参数。图中,理想传输线L被内阻为R0的数字信号驱动源VS驱动,传输线的特性阻抗为Z0,负载阻抗为RL。 理想的情况是当R0=Z0=RL时,传输线的阻抗是连续的,不会发生任何反射,能 ..

[查看全文]

确保信号完整性的电路板设计准则

2012-06-02

16

信号完整性(SI)问题解决得越早,设计的效率就越高,从而可避免在电路板设计完成之后才增加端接器件。SI设计规划的工具和资源不少,本文探索信号完整性的核心议题以及解决SI问题的几种方法,在此忽略设计过程的技术细节。 SI问题的提出 设计前的准备工作 电路板的层叠 串扰和阻抗控制 重要的高速节点 技术选择 预布线阶段 布线后SI仿 ..

[查看全文]

高速PCB设计中的信号完整性分析问答

2012-06-02

23

一、您好:我看到很多SDRAM的数据、地址总线上都串接了小电阻(10欧姆到100欧姆); 1、这样做的主要目的是什么?串接的电阻阻值应该怎么来确定? 2、对于程序FLASH(比如NOR型的flash,access time=70ns)的数据和地址总线需要这样做吗? 不知道你的具体的拓扑结构,我觉得主要是限制信号的反射和过冲的。这要根据你 ..

[查看全文]

高速FPGA系统的信号完整性测试和分析

2012-06-02

张楷

50

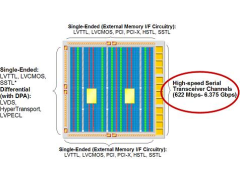

1. 引言 随着FPGA的设计速度和容量的明显增长,当前流行的FPGA芯片都提供高速总线,例如DDR内存总线,PCI-X总线、SPI总线;针对超高速的数据传输,FPGA通过集成SerDes提供高速串行IO,支持各种诸如PCI-E、GBE、XAUI等高速串行总线协议,为各种不同标准的高速传输提供极大的灵活性。典型的高速FPGA器件提供的每一条物 ..

[查看全文]

推荐文章

最新文章

热门文章