Verilog代码编写规范

2012-06-02

12

一. 强调Verilog代码编写风格的必要性。 强调Verilog代码编写规范,经常是一个不太受欢迎的话题,但却是非常有必要的。 每个代码编写者都有自己的编写习惯,而且都喜欢按照自己的习惯去编写代码。与自己编写风格相近的代码,阅读起来容易接受和理解。相反和自己编写风格差别较大的代码,阅读和接受起来就困难一些。 曾有编程大师 ..

[查看全文]

用Verilog-HDL做CPLD设计(时序逻辑电路的实现)

2012-06-02

常晓明 李媛媛

29

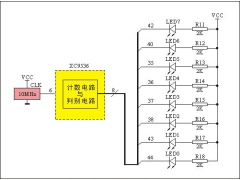

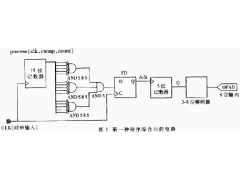

Verilog-HDL与CPLD/FPGA设计应用讲座 第 8 讲 用Verilog-HDL做CPLD设计 时序逻辑电路的实现 8.1 闪烁灯的实现 8.2 流水灯的实现 8.3 可编程单脉冲发生器 在第七讲中,已经介绍了组合逻辑电路的实现。组合逻辑电路的特点是:在任意时刻,电路产生的稳定输出仅与当前时刻的输入有关。时序逻辑电路则不同于它,其特点是:在任意 ..

[查看全文]

VHDL设计中的电路简化问题

2012-06-02

12

摘 要 :从描述方法、设计规则、逻辑函数分析了VHDL设计中容易引起电路复杂化的原因,并提出了相应的解决方法。 近年来,随着集成电路技术的发展,用传统的方法进行芯片或系统设计已不能满足要求,迫切需要提高设计效率。在这样的技术背景下,能大大降低设计难度的VHDL设计方法正越来越广泛地被采用。但是VHDL设计是行为级 ..

[查看全文]

SVPWM信号发生器的VHDL实现

2012-06-02

吴晨光

11

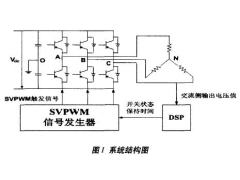

近年来,DSP在SVPWM(空间矢量脉宽调制)控制领域得到了广泛应用。但是使用DSP单核心的控制方法仍然存在一些缺陷:基于软件的:DSP在实现SVPWM触发信号时需要较长的时钟周期;微处理器中不确定的中断响应会导致PWM脉冲的相位抖动。针对以上问题,本文提出了一种利用FPGA实现的SVPWM信号发生器,系统结构如图1所示 ..

[查看全文]

针对C语言编程者的Verilog开发指南

2012-06-02

14

本文举例说明了如何用软件实现脉宽调制(PWM),如何将该设计转换成一个可以在FPGA中运行的逻辑块,并能利用存储器映射I/O接口通过软件完成对该逻辑块的控制。通过理解本文讨论的概念和内容,没有太多硬件知识的软件开发人员也能掌握在FPGA上开发硬件的技能。 在不远的将来,嵌入式系统设计师将能够根据哪个更有利于解决设 ..

[查看全文]

用VHDL设计乐曲发生器

2012-06-02

姜田华

62

1 概述随着EDA 技术的进展,基于可编程 ASIC 的数字电子系统设计的完整方案越来越受到人们的重视,并且以 EDA 技术为核心的能在可编程 ASIC 上进行系统芯片集成的新设计方法,也正在快速地取代基于 PCB板的传统设计方式。 与利用微处理器(CPU 或MCU)来实现乐曲演奏相比,以纯硬件完成乐曲演奏电路的逻辑要复杂得多,如果不 ..

[查看全文]

Verilog-HDL仿真软件ModelSim的基本操作

2012-06-02

常晓明

12

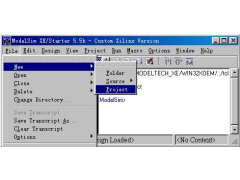

Verilog-HDL与CPLD/FPGA设计应用讲座 第 4 讲 Verilog-HDL仿真软件的基本操作 4.1 建立新的工程文件 4.2 一个最简单的仿真实例 在本讲以Xilinx WebPACK 4.1 ModelSim XE Starter为例,说明仿真软件的基本操作。 4.1 建立新的工程文件 启动Xilinx WebPACK 4.1 ModelSim XE Starter后,选中【File】菜单中的【New】菜单项, ..

[查看全文]

Verilog HDL设计练习进阶(三)

2012-06-02

8

练习三. 利用条件语句实现较复杂的时序逻辑电路 目的:掌握条件语句在Verilog HDL中的使用。 与常用的高级程序语言一样,为了描述较为复杂的时序关系,Verilog HDL提供了条件语句供分支判断时使用。在可综合风格的Verilog HDL模型中常用的条件语句有if…else和case…endcase两种结构,用法和C程序语言中类似。两者相 ..

[查看全文]

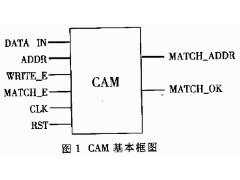

一种基于移位寄存器的CAM的Verilog HDL实现

2012-06-02

10

CAM(Content Addressable Memory,内容可寻址存储器)是一种特殊的存储阵列。它通过将输入数据与CAM中存储的所有数据项同时进行比较,迅速判断出输入数据是否与CAM中的存储数据项相匹配,并给出匹配数据项的对应地址和匹配信息。CAM以其高速查找、大容量等特点而被广泛地应用于电讯、网络等领域。 本文介绍一种用Ve ..

[查看全文]

Verilog中模组(module)的概念

2012-06-02

7

模组(module)的概念 -------------------------------------------------------------------------------- Verilog中的基本单元是模组(module)。 模组代表一些可以用硬体实践的逻辑实体。 例如,一个模组可以是一个逻辑闸、一个三十二位元计数器、一个记忆体子系统、一个机算机系统或是一个用网路相连的多部电脑。 模 ..

[查看全文]

VHDL语言程序配置EAB的研究

2012-06-02

何永泰

59

摘要: 在FPGA(现场可编程门阵列)的使用中,要将VHDL(甚高速集成电路硬件描述语言)编写的程序配置到EAB(嵌入式阵列块)单元中,会遇到许多问题,配置很难成功。根据配置EAB的经验,详细介绍了正确配置EAB的方法。 1、引言 FLEX10K器件是工业界第一个嵌入式的PLD(可编程逻辑器件),由于其具有高密度、低成本、低功率等特点,成 ..

[查看全文]

半整数分频的VHDL程序

2012-06-02

10

想出了一个半整数分频的VHDL语言描述 其实很多问题只要你耐心,也是比较容易的 写出来与大家共享,共同讨论,半整数分频当然还有其他的方法 我认为这种看起来蛮简单的 library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity abc is port(clk:in std_logic; dout:out std_logic); end abc; architecture x ..

[查看全文]

推荐文章

最新文章

热门文章