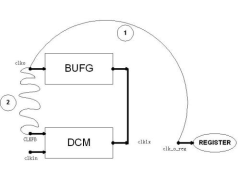

FPGA DCM时钟管理单元的理解

2012-11-01

14

看Xilinx的Datasheet会注意到Xilinx的FPGA没有PLL,其实DCM就是时间管理单元。 ----------------------------------------------------- DCM概述 DCM内部是DLL(Delay Lock Loop(?)结构,对时钟偏移量的调节是通过长的延时线形成的。DCM的参数里有一个PHASESHIFT(相移),可以从0变到255。所以我们可以假设内部结 ..

[查看全文]

Verilog-HDL与CPLD/FPGA设计

2012-10-31

常晓明

44

Verilog-HDL与CPLD/FPGA设计应用讲座 第 1 讲 Verilog-HDL与CPLD/FPGA设计 1.1 从模拟世界到数字世界 1.2 数字电路的不同设计过程 1.3 用HDL描述数字电路 1.4 HDL有几种? 1.5 硬件实现的承担者---CPLD/FPGA 1.6 Xilinx公司的CPLD--XC9500系列 1.7 结语 1.1 从模拟世界到数字世界 在70年代初期,家用电子产品末过于晶体管 ..

[查看全文]

基于FPGA的电阻抗成像系统激励信号源

2012-10-28

王化祥 崔自强

34

电阻抗成像(Electrical Impedance Tomography,EIT)技术是一种廉价的无损伤探测技术,不使用放射源,对人体无害,可作为对患者进行长期、连续监护的医学监护设备. 在医学领域,考虑到患者的安全,激励信号源的电流应小于5 mA;不同人体组织的阻抗随频率变化的特性不同,因此要求激励信号源可以工作在单频、多频或扫频模式下 ..

[查看全文]

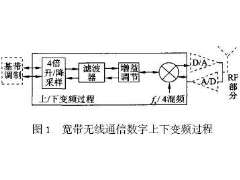

高速上下变频FIR滤波器的FPGA设计

2012-10-27

9

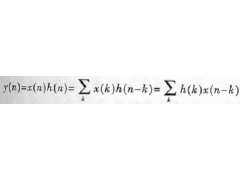

摘要: 针对宽带WLAN 收发器要求, 在单片FPGA 上设计实现了高速数字上下变频器和滤波器, 其中滤波器为80MHz 的40 阶FIR 滤波器, 可以设定工作在上变频或下变频方式。为了对FPGA 的资源占用量最小, 以便实现片上系统(SoC) 设计, 充分利用了上下变频过程中I,Q 数据流的特点, 仅用一套滤波器运算单元分时复用对I,Q 滤波, 同时详 ..

[查看全文]

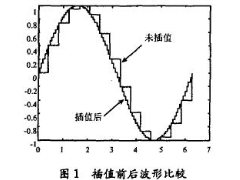

FPGA 在多制式视频转换系统中的应用

2012-10-25

12

1 引言 目前, 在军事、工业和医学领域存在着大量的非标准视频系统, 其视频信号只能在专业的设备上才能播放和录制。而实际中广泛采用的是标准电视信号(PAL ,NTSC, SECAM) 或VGA 视频, 这就给这些领域内的观测监督和学术交流造成了许多困难。以医学信号为例, 目前, 国内医院很多科室的手术监控设备都是国外进口的一体式设备 ..

[查看全文]

用CPU配置FPGA(二)硬件设计

2012-10-25

8

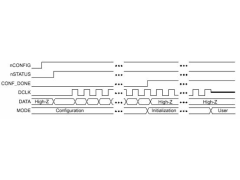

二. 硬件设计 1.配置基本原理 RAM-Based FPGA由于SRAM工艺的特点,掉电后数据会消失。因此,每次系统上电后,均需对FPGA进行配置。对于Altera的FPGA,配置方法可分为:专用的EPROM (Configuration EPROM)、PS(Passive serial 无源串行)、PPS(Passive parallel synchronous 无源同步并行)、PPA(Passive para ..

[查看全文]

基于FPGA 的高速实时FFT处理器设计

2012-10-22

周海斌 刘刚

13

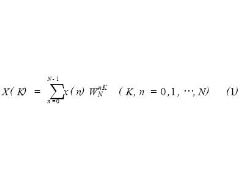

离散傅里叶变换(DFT) 是数字谱分析必需的变换工具。完成N 点DFT 运算约需N2 次乘法和N(N-1) 次加法,当N 较大时,运算量非常大,使其实际应用受到极大的限制。快速傅里叶变换(FFT) 采用递归型算法,利用旋转因子的周期性和对称性,将长序列DFT 分解为短序列DFT ,使总运算量减小1~2 个数量级,从而大大加快了运算速度。FFT 和 ..

[查看全文]

FPGA 可编程全数字锁相环路的实现

2012-10-22

12

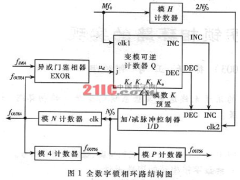

锁相环路已在模拟和数字通信及无线电电子学等各个领域中得到了极为广泛的应用,特别是在数字通信的调制解调和位同步中常常要用到各种各样的锁相环。锁相就是利用输入信号与输出信号之间的相位误差自动调节输出相位使之与输入相位一致,或保持一个很小的相位差。最初的锁相环全部由模拟电路组成,随着大规模、超高速数字集成 ..

[查看全文]

数字频率合成器的FPGA实现

2012-10-21

潘毅 李栋 龚建荣

10

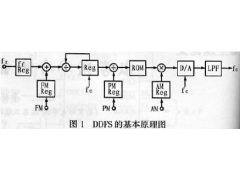

摘要:介绍了DDFS的原理和Altera公司的FPGA器件ACEX 1K的主要特点,给出了用ACEX 1K系列器件EP1K10TC144-1实现数字频率合成器的工作原理、设计思路、电路结构和仿真结果。 1 概述 1971年,美国学者J.Tierncy,C.M.rader和B.Gold提出了以全数字技术,从相位概念出发直接合成所需波形的一种新的频率合成方法。限于当时的 ..

[查看全文]

FIR数字滤波器分布式算法的原理及FPGA实现

2012-10-16

9

摘要: 在利用FPGA实现数字信号处理方面,分布式算法发挥着关键作用,与传统的乘积-积结构相比,具有并行处理的高效性特点。详细研究了基于FPGA、采用分布式算法实现FIR数字滤波器的原理和方法,并通过Xilinx ISE在Modelsim下进行了仿真。 关键词: 分布式算法 DALUT FPGA FIR 数字滤波器正在迅速地代替传统的由R、L、C元件 ..

[查看全文]

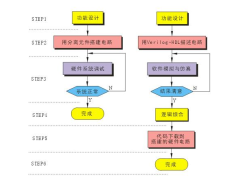

基于IP核的FPGA 设计方法

2012-10-15

陈文艺

12

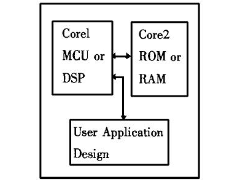

摘要:随着集成电路制造技术迅速向亚微米发展, 产生了系统级集成的新概念, 为缩短系统级芯片的设计时间, 重复利用已有的设计, 核基设计方法被广泛采用。本文介绍了核的分类及核基FPGA 的设计流程, 讨论了软核的设计思路和使用特点, 并给出了设计实例。 前 言 几年前设计专用集成电路(ASIC) 还是少数集成电路设计工程师的事, 随 ..

[查看全文]

推荐文章

最新文章

热门文章