嵌入式系统BootLoader技术内幕

2012-06-11

詹荣开

11

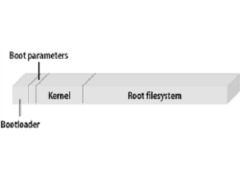

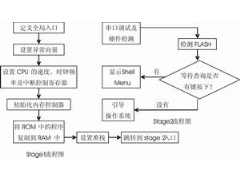

本文详细地介绍了基于嵌入式系统中的 OS 启动加载程序 ―― Boot Loader 的概念、软件设计的主要任务以及结构框架等内容。 在专用的嵌入式板子运行 GNU/Linux 系统已经变得越来越流行。一个嵌入式 Linux 系统从软件的角度看通常可以分为四个层次: 1. 引导加载程序。 包括固化在固件(firmware)中的 boot 代码(可选),和 Boot L ..

[查看全文]

增量累加ADC以高24位的精确度测量小模拟信号

2012-06-02

15

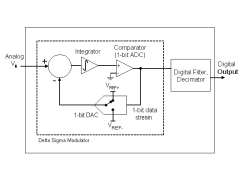

一个量程10千克的秤若能分辨出1克的重量变化,那么这个秤的主要组件常常是增量累加模数转换器。设计师需要温度测量的精确度达到0.01度时,增量累加ADC也常常成为首选方案。增量累加ADC还能够取代那些前面加有一个增益级的传统型逐次逼近寄存器ADC。由于这些数据转换器非常适用于量度真实世界的微小变化,所以温度传感器 ..

[查看全文]

从实例中学习OrCAD-PSpice 10.3-AA(第6章 蒙特卡洛工具...

2012-06-02

35

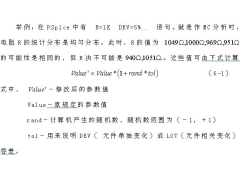

第6章 蒙特卡洛(Monte Carlo)工具的使用 PSpice一直重视所设计的电路,要能适合于批量生产的需要。现在PSpice10.3单独设立Monte Carlo工具,使这一项工作得到加强。本章先简介容差分析的基本概念,其后重点介绍Monte Carlo工具的使用方法。 6.1容差分析 前几章所述电路分析法时,已经提过只将元件视作理想元件按标称值进 ..

[查看全文]

Cadence的 EDA验证工具在 SOC设计中的应用

2012-06-02

叶 辉

12

摘要: 本文介绍了Cadence公司的NC-Verilog/Verilog-XL Simulator以及Signalscan在SOC设计中的应用。 关键词: SOC,协同验证(co-verification) 在ASIC 和 SOC 设计中,验证是极为重要的一环,Cadence公司的NC-Verilog仿真器(以及较早产品 Verilog-XL)是用来仿真用 Verilog 语言写的数字逻辑电路。该仿真器在 ASIC和SO ..

[查看全文]

从实例中学习OrCAD-PSpice 10.3-AA(第7章 电应力工具)

2012-06-02

24

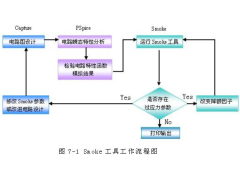

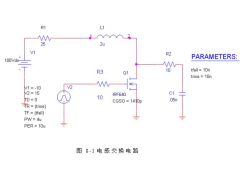

第7章 电应力(Smoke)工具的使用 电子电路在工作过程中,常因某(些)个元器件承受的热电应力超出其安全工作条件,降低其可靠性,严重地导致冒烟烧毁。因此,“冒烟报警”提高电路工作的可靠性,对一些安全性要求较高的电路(网络)采用降额设计已纳入电子工程师视野。本章结合电路实例简介可靠性、降额设计的基 ..

[查看全文]

从实例中学习OrCAD-PSpice 10.3-AA(第8章 参数测绘仪工...

2012-06-02

21

第8章 参数测绘仪(Parametric Plotter)工具的使用 参数测绘仪工具不但可以进行多种复杂参数功能的扫描,还可以在Plot/Probe中通过表格与绘图形式更美观和有效的分析扫描结果。用户可以在创建和参数测绘仿真电路时,运用参数测绘仪来进行设计和相关参数模型的分析(任何结合部分)。也可以说参数测绘仪工具是标准PSPICE参 ..

[查看全文]

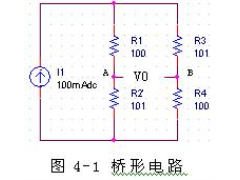

从实例中学习OrCAD-PSpice 10.3-AA(第4章灵敏度分析工具)

2012-06-02

22

想要调用PSpice–AA进行电路优化设计,一般是先进行灵敏度(Sensitivity)分析:以便确定电路中对电路特性影响最大的关键元件参数进行优化。OrCAD9.2以前版本的灵敏度分析,由于有大量数据输出问题没有解决,故只局限于作直流灵敏度分析,置于直流工作点分析内。 直流灵敏度分析:虽然电路特性完全取决于电路中的元器 ..

[查看全文]

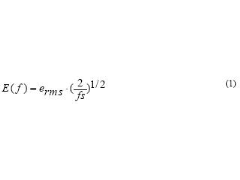

基于过采样技术提高ADC分辨率的研究与实现

2012-06-02

李国

22

很多应用场合需要使用模/数转换器ADC 进行参数测量,这些应用所需要的分辨率取决于信号的动态范围、必须测量的参数的最小变化和信噪比SNR。许多系统中既有很宽的动态范围又要求测量出参数的微小变化,因此就必须使用高分辨率的ADC。然而,高分辨率的ADC 器件价格昂贵,若使用价格相对低廉的具有较低分辨率的ADC 器件,通 ..

[查看全文]

ADC0809 VHDL控制程序

2012-06-02

50

--文件名:ADC0809.vhd --功能:基于VHDL语言,实现对ADC0809简单控制 --说明:ADC0809没有内部时钟,需外接10KHz~1290Hz的时钟信号,这里由FPGA的系 --统时钟(50MHz)经256分频得到clk1(195KHz)作为ADC0809转换工作时钟。 --最后修改日期:2004.3.20 library ieee; use ieee.std_logic_1164.all; use ieee.std ..

[查看全文]

Linux bootloader编写方法

2012-06-02

范晓炬

12

对于移植 linux 到其它开发板的人来说,编写 boot loader 是一个不可避免的过程。对于学习 linux的人来讲,编写 bootloader 也是一个很有挑战性的工作。本文通过对 linux引导协议进行分析,详细阐述了如何编写一个可以在i386 机器上引导 2.4.20内核的基本的bootloader。 1.概述 linux运行在保护模式下,但是当机器启动复位的时候却 ..

[查看全文]

从实例中学习OrCAD-PSpice 10.3-AA(第一章 安装)

2012-06-02

44

第1章 安装 OrCAD 10.3 Release1.1 OrCAD 10.3 Release安装建议的计算机配置1.1.1 OrCAD 10.3 Release 窗口操作系统OrCAD 10.3 Release可以执行在下列2 种Microsoft 窗口操作系统:(1)Windows 2000(SP4)(2)Windows XP Professional, or Windows XP Home Edition注:OrCAD10.3 Release已不再支持Windows NT 窗 ..

[查看全文]

S3C44B0X上的一款Boot Loader解析

2012-06-02

李娜 许童羽 李征明

15

摘要: 本文对Boot Loader的功能、操作模式等作了简单的介绍,重点对基于S3C44B0X内核的UP-NetARM3000上移植uCOS所设计的Boot Loader代码进行了深入的分析和研究,详细的介绍了这款Boot Loader的运行流程和工作机理,为成功装载嵌入式操作系统建立良好的软硬件环境。 一个完整的嵌入式系统包括嵌入式微处理器和外围支 ..

[查看全文]

推荐文章

最新文章

热门文章