Verilog阻塞式赋值与非阻塞式赋值的分析

2012-06-02

nsun

19

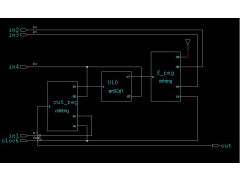

在Verilog HDL中,有两种过程性赋值方式,即阻塞式(blocking)和非阻塞式(non-blocking)。这两种赋值方式看似差不多,其实在某些情况下却有着根本的区别,如果使用不当,综合出来的结果和你所想得到的结果会相去甚远。 Tip:所谓过程性赋值就是指在initial或always语句内的赋值,它只能对寄存器数 据类型的变量赋值。 阻塞式 ..

[查看全文]

用Verilog-HDL做CPLD设计(组合逻辑电路的实现)

2012-06-02

李媛媛 常晓明

9

Verilog-HDL与CPLD/FPGA设计应用讲座 第 7 讲 用Verilog-HDL做CPLD设计 组合逻辑电路的实现 7.1 与非门的实现 7.2 2-1数据选择器的实现 7.3 2位二进制编码器的实现 7.4 1位数据比较器的实现 本讲中,我们通过由浅入深的实例来介绍组合逻辑电路在目标板上是如何实现的。 7.1 与非门的实现 首先,来实现一个用两个开关控制一个灯的 ..

[查看全文]

SPI串行总线接口的Verilog实现

2012-06-02

孙丰军 余春暄

16

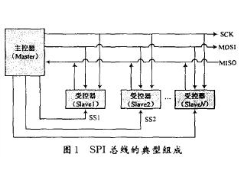

摘 要:集成电路设计越来越向系统级的方向发展,并且越来越强调模块化的设计。SPI(Serial Peripheral Bus)总线是Motorola公司提出的一个同步串行外设接口,容许CPU 与各种外围接口器件以串行方式进行通信、交换信息。本文简述了SPI总线的特点,介绍了其4条信号线,SPI串行总线接口的典型应用。重点描述了SPI串行总线接口在一款 ..

[查看全文]

verilog的键盘源码keypad—有去抖功能

2012-06-02

11

下面是转的一个源码,俺没有细看,有兴趣的看看,讲讲如何 // author: Dandy Nee // mail:dandynee@yeah.net // module: HW KeyScan Module // version:0.1 // ************************** // all functions are provided as if okay // run at your own risk // ************************** // // problem:there is one keyva ..

[查看全文]

fir滤波器的Verilog程序

2012-06-02

35

`timescale 1ns / 1ps //////////////////////////////////////////////////////////////////////////////// // Company: // Engineer: // // Create Date:17:01:38 10/09/06 // Design Name: // Module Name:ppeifir // Project Name: // Target Device: // Tool versions: // Description:用Verilog编写的fir滤波器程 ..

[查看全文]

用Verilog HDL设计自动数据采集系统

2012-06-02

11

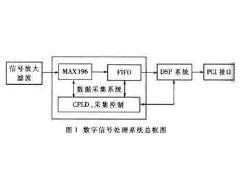

随着数字时代的到来,数字技术的应用已经渗透到了人类生活的各个方面。数字系统的发展在很大程度上得益于器件和集成技术的发展,著名的摩尔定律(Moore's Law)的预言也在集成电路的发展过程中被印证了,数字系统的设计理念和设计方法在这过程中发生了深刻的变化。从电子CAD、电子CAE到电子设计自动化(EDA ..

[查看全文]

推荐文章

最新文章

热门文章