modelsim学习笔记

2012-10-10

16

1. 建一个总文件夹,如cnt 2. 为源代码,测试台文件,仿真各建一文件夹。如src,tb,sim 3. 编写源代码,testbench。如cnt.v,tb_cnt.v文件,同时文件名里的模块名与文件名相同,如modulecnt(), moduletb_cnt()。 4. 再sim文件夹里加入tb.f文件:../tb/tb_cnt.v ../src/cnt.v ../tb/tb_cnt-y ../src+libext+.v(这里源代码 ..

[查看全文]

Modelsim 包会教程

2012-10-10

Timothy.Lee

10

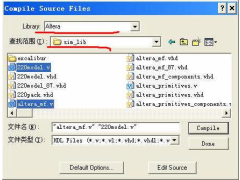

Modelsim是现在业界比较流行的HDL语言仿真工具。在这里关于他的使用我就不说了。主要是讲一讲困扰我们的库编译的问题。 因为Modelsim为各个主要fpga厂商都提供了支持,所以在我们使用的时候必须先要对相应的厂商的库进行编译。在这里,我以xilinx公司为例。使用的软件为ise5.2i,modelsim se 5.7c(如果版本不同,并不影响 ..

[查看全文]

ModelSim SE操作指南

2012-07-03

31

第一章 介绍 本指南是为 ModelSim5.5f版本编写的,该版本运行于UNIX和Microsoft Windows 95/98/Me/NT/2000的操作系统环境中。本指南覆盖了VHDL和Verilog模拟仿真,但是你在学习过程中会发现对于单纯的HDL设计工作而言,它是一个很有用的参考。ModelSim具备强大的模拟仿真功能,在设计、编译、仿真、测试、调试开发过 ..

[查看全文]

Verilog Pli的基本使用方法(modelsim)

2012-06-02

17

内容未做证实,仅供参考。 1.hello.c文件内容 #include #include "veriuser.h" static PLI_INT32 hello() { printf("Hi there\n"); return 0; } s_tfcell veriusertfs[] = { {usertask, 0, 0, 0, hello, 0, "$hello"}, {0} /* last entry must be 0 */ }; 2.hello.v文件内容 module hello; initial begin $hello ..

[查看全文]

Verilog-HDL仿真软件ModelSim的基本操作

2012-06-02

常晓明

12

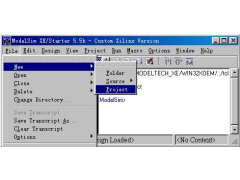

Verilog-HDL与CPLD/FPGA设计应用讲座 第 4 讲 Verilog-HDL仿真软件的基本操作 4.1 建立新的工程文件 4.2 一个最简单的仿真实例 在本讲以Xilinx WebPACK 4.1 ModelSim XE Starter为例,说明仿真软件的基本操作。 4.1 建立新的工程文件 启动Xilinx WebPACK 4.1 ModelSim XE Starter后,选中【File】菜单中的【New】菜单项, ..

[查看全文]

关于modelsim的使用

2012-06-02

17

由于modelsim命令模式查看波形不方便,所以我们在仿真结束后查看波形进行查看,就需要存储波形。下面是网上的一点东西,给我的仿真带来了方便。 VCD system task calls in the Verilgsource code. .可以通过在源代码中添加语句来实现 initial begin $Dumpfile("./test.fsdb"); $Dumpvars(0,test); #60000000 $finis ..

[查看全文]

利用ModelSim SE6.0C实现时序仿真

2012-06-02

16

1) 打开一个工程文件。 2) 打开Settings设置栏,选择EDA Tools Settings下的Simulation栏。在右边出现的设置栏中将“Tool name”的下拉菜单选择“ModelSim(Verilog)”(如果工程用VHDL语言实现,则可以选择“ModelSim(VHDL)”;如果ModelSim使用的是for Altera的专用版本,则可以选择 ..

[查看全文]

modelsim仿真ROM

2012-06-02

8

一、主要环境参数是 : modelsim SE 6.1b+Quartus II 5.1 SP2 HDL 是verilog。 器件是Stratix II EP2S90F1020 采用两种方法设计ROM,ROM的容量是1000×2×16bit。因为需要COS 和SIN 两种数据。 第一种采用Altera 的LPM 生成ROM,ROM 的内容也是利用Quartus 生成hex 文件,之所以不采用mif 文件的原因是因为在modelsim不 ..

[查看全文]

ModelSim SE仿真Altera库的建立

2012-06-02

shemily

25

(注:最近自己准备做后仿真,到坛子里看看了,发现一开始建库就是一个很大的问题。为了便以自己学习也为了给大家省点事,我花了十来个小时整理了一些资料,全部资料来自edacn.net/bbs的ModelSim的〈库〉,在下面的资料中不能一一列出作者,请各位网友多多包涵。下面的资料是大家的成果。by CHY 07.04.05) 1. modelsim怎 ..

[查看全文]

基于 Modelsim FLI 接口的FPGA仿真技术

2012-06-02

胡军强 李津生 洪佩琳

8

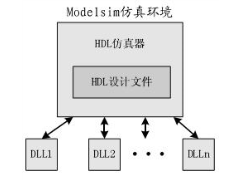

摘要:本文介绍了如何利用modelsim提供的FLI(Foreign Language Interface)接口进行VHDL设计文件的协同仿真,给出了协同仿真的意义以及协同仿真的程序结构和系统结构。 关键词:FPGA,仿真软件,协同仿真 1、Modelsim 及 FLI接口介绍 Modelsim是 Model Technology(Mentor Graphics的子公司)的 HDL 硬件描述语言仿真 ..

[查看全文]

debussy和modelsim协同仿真(VHDL)

2012-06-02

22

1、 编辑modelsim根目录下的modelsim.ini文件,将; Veriuser = veriuser.sl 更换为Veriuser = novas_fli.dll。 2、 将C:\Novas\Debussy\share\PLI\modelsim_fli54\WINNT下的novas_fli.dll 拷贝至C:\Modeltech_6.1d\win32中 3、 将C:\Novas\Debussy\share\PLI\modelsim_fli54\WINNT下的novas.vhd拷贝至工程所在目录 4、 ..

[查看全文]

ISE仿真中需要注意的问题

2012-06-02

iamfrankie

14

在我们团队负责的项目光栅传感器系统高频并行解调算法的FPGA实现中,需要直接频率合成模块,因此我们想在FPGA上实现一个DDS芯片的功能,最近在BASYS板上调通了DDS模块,在功能仿真过程中我们发现在ISE环境下编写VHDL时对信号赋初值对仿真是十分必要的。 由于参数的要求模块中用到了一个三分频电路。程序如下: library ..

[查看全文]

推荐文章

最新文章

热门文章