Verilog串口通讯设计

2013-03-11

11

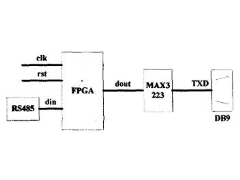

1 串口通信基本特点 随着多微机系统的应用和微机网络的发展,通信功能越来越显得重要。串行通信是在一根传输线上一位一位地传送信息.这根线既作数据线又作联络线。串行通信作为一种主要的通信方式,由于所用的传输线少,并且可以借助现存的电话网进行信息传送,因此特别适合于远距离传送。在串行传输中,通信双方都按通信协议 ..

[查看全文]

八位的伪随机数产生的verilog源程序

2013-03-11

11

linear-feedback-shift-register 下面是一个八位的伪随机数产生的verilog文件,我想够用了。 // DEFINES `timescale 1ns/1ns `define DEL1// Clock-to-output delay. Zero // time delays can be confusing // and sometimes cause problems. // These are good tap values for 2 to 32 bits `define TAP22'b11 `define TAP33' ..

[查看全文]

VHDL设计MOORE型有限状态机时速度问题的探讨

2013-03-10

朱小莉 陈迪平 王镇道

22

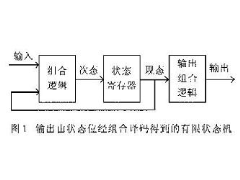

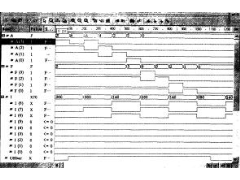

1 引言 随着微电子技术的迅速发展,人们对数字系统的需求也在提高。不仅要有完善的功能,而且对速度也提出了很高的要求。对于大部分数字系统,都可以划分为控制单元和数据单元两个组成部分。通常,控制单元的主体是一个有限状态机,它接收外部信号以及数据单元产生的状态信息,产生控制信号序列。MOORE型有限状态机的设计方 ..

[查看全文]

带进位加法器之VHDL描述

2013-03-09

skycanny

22

学过VHDL的人都知道,VHDL是提供了操作符“+”,而且在很多情况下,我们是可以直接用这个加操作符的。但是,VHDL提供的加法操作只能给出 “和”,却无法给出“进位”。例如我们在设计计数器的时候经常用到的加1操作,对于一个8位的计数器,当计数器的结果为0xff时,如果在加1就为 0x0 ..

[查看全文]

Verilog-HDL的基本概念

2013-03-09

常晓明

13

Verilog-HDL与CPLD/FPGA设计应用讲座 第 3 讲 Verilog-HDL的基本概念 3.1 与门的描述 3.2 与非门的描述 3.3 非门的描述 3.4 或门的描述 3.5 或非门的描述 3.6 缓冲器的描述 3.7 逻辑仿真与测试模块 3.1 与门的描述 让我们通过最简单的例子来认识一下Verilog-HDL的基本用法。 (1)模块的定义 用Verilog-HDL做数字电路描述,一开始所 ..

[查看全文]

可提高设计性能的HDL编程风格与技巧

2013-03-05

17

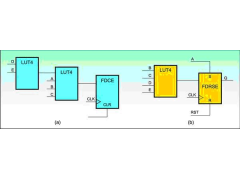

通过熟悉器件架构,选择合适的硬件平台和硅片特性,并借助配置恰当且性能优良的实现工具,设计人员就能获得较高的设计性能。不过,在提高设计性能的众多方法中最容易被忽视的也许就是为目标器件编写高效的HDL代码。本文所讨论的编程风格与技巧可提高设计性能。使用复位对性能的影响 很少有哪种系统级的选择能够像复位选择那 ..

[查看全文]

利用FPGA驱动LCD显示中文字符“年”的VHDL程序

2013-02-23

14

--文件名:lcd_driver.vhd。 --功能:FGAD驱动LCD显示中文字符“年”。 --最后修改日期:2004.3.24。 library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity lcd_driver is Port ( clk : in std_logic; --状态机时钟信号,同时也是液晶时钟 ..

[查看全文]

双向数据转换器的VHDL程序设计

2013-02-22

朱海君 衡昌胜 敬岚

16

摘 要 :VHDL(超高速集成电路硬件描述语言)目前在电子设计领域得到了广泛应用。本文介绍了使用VHDL语言实现CPLD设计的方法,并以此方法在ALTERA公司的CPLD器件 EPM7128SQC100-10上实现8位到32位的双向数据转换器芯片。 关键词 :VHDL,CPLD,数据转换器,设计 引言 随着CPLD(Complex Programmable Logic Device)、 ..

[查看全文]

VHDL设计举例:直流电机控制器

2013-02-17

25

LIBRARY IEEE; USE IEEE.std_logic_1164.ALL; USE IEEE.std_logic_unsigned.all; USE IEEE.std_logic_arith.all; ENTITY dccount IS port ( clk: IN STD_LOGIC; AI : IN STD_LOGIC_VECTOR(3 DOWNTO 0); CO : out STD_LOGIC_VECTOR(3 DOWNTO 0); pulse: IN STD_LOGIC; driverA,driverB: OUT STD_LOGIC; S : OUT S ..

[查看全文]

用verilog编写的多功能数字钟

2013-02-08

8

/* 信号定义: clk: 标准时钟信号,本例中,其频率为4Hz; clk_1k: 产生闹铃音、报时音的时钟信号,本例中其频率为1024Hz; mode: 功能控制信号; 为0:计时功能; 为1:闹钟功能; 为2:手动校时功能; turn: 接按键,在手动校时功能时,选择是调整小时,还是分钟; 若长时间按住该键,还可使秒信号清零,用于精确调时; chan ..

[查看全文]

4位除法器vhdl程序

2013-02-06

16

4位除法器,vhdl -- -- --------------------------------------------------------------------------------/ -- DESCRIPTION : Signed divider -- A (A) input width : 4 -- B (B) input width : 4 -- Q (data_out) output width : 4 -- DIV_BY_0 (DIVz) output active : high -- Download from : http://www.pld.com.c ..

[查看全文]

VHDL应用于专用集成电路功能仿真的研究

2013-02-02

10

摘要:研究了如何对一个ASIC 系统(以8051微控制器为例)应用VHDL进行功能仿真的方法,在ACTIVE-VHDL软件环境下应用该语言编制了8051微控制器的功能仿真程序并进行了测试。测试结果表明该程序运行是正确的。本文给出的方法在ASIC的高层次设计上迈出了重要的一步,在工程实践中具有广泛的应用价值。 0 引言 VHDL(VSHIC H ..

[查看全文]

推荐文章

最新文章

热门文章