Verilog电话计费器的代码

2013-01-15

16

/*信号定义: clk:时钟信号,本例中其频率值为1Hz; decide:电话局反馈回来的信号,代表话务种类,“01”表示市话,“10”表示 长话,“11”表示特话; dispmoney: 用来显示卡内余额,其单位为角,这里假定能显示的最大数额为50元(500角); disptime:显示本次通话的时长; write,r ..

[查看全文]

verilog综合小结

2013-01-08

4

一:基本 Verilog中的变量有线网类型和寄存器类型。线网型变量综合成wire,而寄存器可能综合成WIRE,锁存器和触发器。 二:verilog语句结构到门级的映射 连续性赋值:assign 连续性赋值语句逻辑结构上就是将等式右边的驱动左边的结点。因些连续性赋值的目标结点总是综合成由组合逻辑驱动的结点。Assign语句中的延时综合时都将忽 ..

[查看全文]

Verilog语言综合问题研究

2013-01-05

何清平 刘佐濂 江建钧

15

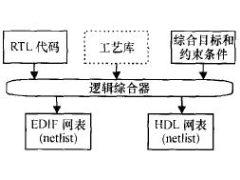

摘要:综合问题是FPGA设计过程中的关键环节,综合的结果就是系统设计的硬件结构,决定了系统的性能.文章通过RTI 电路模型来分析代码风格对综合结果的影响,介绍了著名的DC综合器的综合约束模型.为FPGA设计者提供最佳的综合设计策略. 随着计算机技术和微电子技术的发展,ASIC(Application Specific Integrated Circuit,专用 ..

[查看全文]

用Verilog语言描述一个双向端口

2013-01-03

8

对双向端口,我们可以将其理解为2个分量:一个输入分量,一个输出分量。另外还需要一个控制信号控制输出分量何时输出。此时,我们就可以很容易地对双向端口建模。 例子: CODE: module dual_port ( .... inout_pin, .... ); inout inout_pin; wire inout_pin; wire input_of_inout; wire output_of_inout; wire out_en; assign input_ ..

[查看全文]

构筑Verilog-HDL设计所需要的环境

2012-12-27

常晓明

11

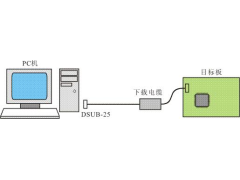

Verilog-HDL与CPLD/FPGA设计应用讲座 第 2 讲 构筑Verilog-HDL设计所需要的环境 2.1 进行Verilog-HDL设计需要什么样的环境? 2.2 软件的获取与安装 2.3 下载电缆与目标板 2.4 目标板 2.5 结语 2.1 进行Verilog-HDL设计需要什么样的环境? 2.1.1 硬件环境 要进行Verilog-HDL设计,首要的环境就是硬件环境。图1给出了进行Verilog ..

[查看全文]

Verilog 非阻塞赋值的仿真/综合问题

2012-12-27

17

源文件作者:Clifford E. Cummings(Sunburst Design, Inc.)原标题:Nonblocking Assignments in Verilog Synthesis, Coding Styles That Kill! ATTN:所有括号内“外注”为理解方便或有疑问的地方,原文里并没有。所有翻译都是为遵循“共同进步”的理想但并没有去努力得到原作者的任何书面和其它方式 ..

[查看全文]

Candence混合仿真(spectre verilog)的一点心得

2012-12-25

31

1、IO口的问题。 在Candence的混合仿真好像对IO口的支持不是很好,我在使用的过程中是将IO口改为input口,再把电路中的output回路断开。模拟完成以后,看output回路中的信号,从而判断电路的out是否正常。至于Candence的混合仿真是不是支持IO 口,还要进一步的摸索。 2、verilog的作用。 在这次仿真过程中,我总结出了verilo ..

[查看全文]

基于Verilog HDL语言的32X8 FIFO设计

2012-12-24

夏传红 王祖强 李秀娟

12

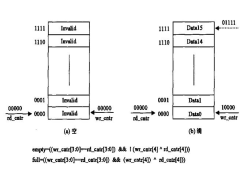

摘要:介绍了FIFO的基本概念、设计方法和步骤,采用了一种新颖的读、写地址寄存器和双体存储器的交替读、写机制,实现了FIFO的基本功能,同时使本32X8 FIFO拥有可同时读、写的能力,完全基于Verilog HDL语言实现了电路功能并应用Synopsys公司的DesignCompiler和VCS对其进行综合、仿真。 对基于单体存储器的FIFO,作为一种数据 ..

[查看全文]

Verilog HDL设计练习进阶(十)

2012-12-20

8

练习十. 通过模块之间的调用实现自顶向下的设计 目的:学习状态机的嵌套使用实现层次化、结构化设计。 现代硬件系统的设计过程与软件系统的开发相似,设计一个大规模的集成电路的往往由模块多层次的引用和组合构成。层次化、结构化的设计过程,能使复杂的系统容易控制和调试。 在Verilog HDL中,上层模块引用下层模块与C语言中 ..

[查看全文]

用Verilog-HDL做CPLD设计(目标板的设计和下载软件的使用)

2012-12-15

李媛媛 常晓明

9

Verilog-HDL与CPLD/FPGA设计应用讲座 第 6讲 用Verilog-HDL做CPLD设计 目标板的设计和下载软件的使用 6.1 目标板的制作 6.2 一个最简单的设计 6.3 一个最简单设计的实现--下载实例 6.1 目标板的制作 学习了Verilog-HDL的基本概念,并用其仿真环境Modelsim XE对基本逻辑电路进行仿真后,如果希望在硬件上实现所设计的电路功能 ..

[查看全文]

verilog PS2键盘解码程序

2012-12-10

11

之前探讨过PS/2键盘编解码以及数据传输协议,这次自己动手实现了利用FPGA接收键盘编码,然后通过串口传输到PC。做的比较简单,只是通过FPGA把大写字母A-Z转换成相应的ASCII码,只要字母按键被按下,就能在串口调试助手里显示相应大写字母。下面就共享代码吧! 除了顶层模块,三个底层模块分别为PS/2传输处理模块、串口传 ..

[查看全文]

Ncverilog 的一些经验

2012-12-08

17

1.Verilog和Ncverilog命令使用库文件或库目录 ex). ncverilog -f run.f -v lib/lib.v -y lib2 +libext+.v//一般编译文件在run.f中, 库文件在lib.v中,lib2目录中的.v文件系统自动搜索 使用库文件或库目录,只编译需要的模块而不必全部编译 2.Verilog Testbench信号记录的系统任务: 1). SHM数据库可以记录在设计仿真过程中信号的变化. ..

[查看全文]

推荐文章

最新文章

热门文章