高速PCB设计入门概念问答

2012-10-22

13

要做高速的PCB设计,首先必须明白下面的一些基本概念,这是基础。 1、什么是电磁干扰(EMI)和电磁兼容性(EMC)? (Electromagnetic Interference),有传导干扰和辐射干扰两种。 传导干扰是指通过导电介质把一个电网络上的信号耦合(干扰)到另一个电网络。辐射干扰是指干扰源通过空间把其信号耦合(干扰)到另一个电网络。 ..

[查看全文]

高速PCB设计指南(五)

2012-10-15

17

第一篇DSP系统的降噪技术随着高速DSP(数字信号处理器)和外设的出现,新产品设计人员面临着电磁干扰(EMI)日益严重的威胁。早期,把发射和干扰问题称之为EMI或 RFI(射频干扰)。现在用更确定的词“干扰兼容性”替代。电磁兼容性(EMC)包含系统的发射和敏感度两方面的问题。假若干扰不能完全消除,但也要使干扰减少到 ..

[查看全文]

SI高速电路设计:高速PCB设计理论基础

2012-10-09

阿鸣

13

第一部分信号完整性知识基础 第一章高速数字电路概述 现代的电子设计和芯片制造技术正在飞速发展,电子产品的复杂度、时钟和总线频率等等都呈快速上升趋势,但系统的电压却不断在减小,所有的这一切加上产品投放市场的时间要求给设计师带来了前所未有的巨大压力。要想保证产品的一次性成功就必须能预见设计中可能出现的各种问 ..

[查看全文]

高速PCB设计指南(四)

2012-10-09

23

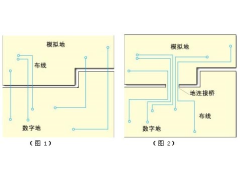

一、印制电路板的可靠性设计目前电子器材用于各类电子设备和系统仍然以印制电路板为主要装配方式。实践证明,即使电路原理图设计正确,印制电路板设计不当,也会对电子设备的可靠性产生不利影响。例如,如果印制板两条细平行线靠得很近,则会形成信号波形的延迟,在传输线的终端形成反射噪声。因此,在设计印制电路板的时候 ..

[查看全文]

高速PCB设计指南(一)

2012-07-25

47

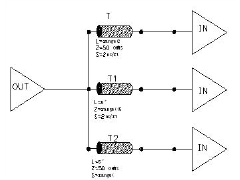

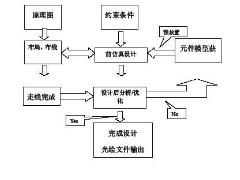

第一篇 PCB布线在PCB设计中,布线是完成产品设计的重要步骤,可以说前面的准备工作都是为它而做的,在整个PCB中,以布线的设计过程限定最高,技巧最细、工作量最大。PCB布线有单面布线、双面布线及多层布线。布线的方式也有两种:自动布线及交互式布线,在自动布线之前,可以用交互式预先对要求比较严格的线进行布 ..

[查看全文]

高速PCB设计指南(二)

2012-07-25

45

第一篇 改进电路设计规程提高可测试性 随着微型化程度不断提高,元件和布线技术也取得巨大发展,例如BGA外壳封装的高集成度的微型IC,以及导体之间的绝缘间距缩小到0.5mm,这些仅是其中的两个例子。电子元件的布线设计方式,对以后制作流程中的测试能否很好进行,影响越来越大。下面介绍几种重要规则及实用提示。 通过遵守 ..

[查看全文]

高速PCB设计EMI规则探讨

2012-07-03

51

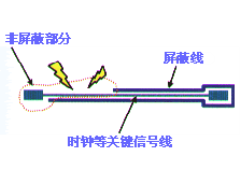

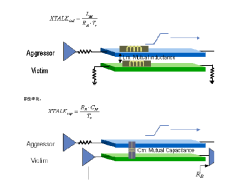

随着信号上升沿时间的减小,信号频率的提高,电子产品的EMI问题,也来越受到电子工程师的光注。高速PCB设计的成功,对EMI的贡献越来越受到重视,几乎60%的EMI问题可以通过高速PCB来控制解决。做了4年的EMI设计,一些心得和大家交流、交流。 规则一:高速信号走线屏蔽规则 如上图所示:在高速的PCB设计中,时钟等关键的 ..

[查看全文]

电容在高速PCB设计中的应用

2012-06-02

18

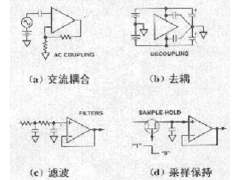

探讨高速PCB设计电容的应用。电容是电路板上不可缺少的一个部分,并且起到了至关重要的作用,探讨它具备至关重要的价值。您在设计中是否有这样困惑:我要用什么样的电容?需要多少这样电容?要如何放置这样的电容?带着这些疑问我们走入我们的正题笫—部分、电容的分类电容在电路的设计中从应用上进行分类,可以将电容分为四类 ..

[查看全文]

高速PCB设计中的信号完整性分析问答

2012-06-02

23

一、您好:我看到很多SDRAM的数据、地址总线上都串接了小电阻(10欧姆到100欧姆); 1、这样做的主要目的是什么?串接的电阻阻值应该怎么来确定? 2、对于程序FLASH(比如NOR型的flash,access time=70ns)的数据和地址总线需要这样做吗? 不知道你的具体的拓扑结构,我觉得主要是限制信号的反射和过冲的。这要根据你 ..

[查看全文]

推荐文章

最新文章

热门文章