DSP高速PCB抗干扰设计

2013-01-01

刘金锁

46

随着DSP(数字信号处理器)的广泛应用,基于DSP的高速信号处理PCB板的设计显得尤为重要。在一个DSP系统中,DSP微处理器的工作频率可高达数百MHz,其复位线、中断线和控制线、集成电路开关、高精度A/D转换电路,以及含有微弱模拟信号的电路都非常容易受到干扰;所以设计开发一个稳定的、可靠的DSP系统,抗干扰设计非常重 ..

[查看全文]

高速PCB设计指南(六)

2012-12-29

42

第一篇混合信号电路板的设计准则模拟电路的工作依赖连续变化的电流和电压。数字电路的工作依赖在接收端根据预先定义的电压电平或门限对高电平或低电平的检测,它相当于判断逻辑状态的 “真”或“假”。在数字电路的高电平和低电平之间,存在“灰色”区域,在此区域数字电路有时表现出模拟效应,例如当从低电平向高电平(状态) ..

[查看全文]

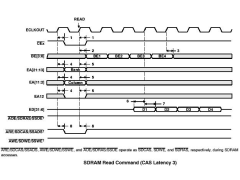

Cadence 高速PCB的时序分析(2)

2012-12-27

22

列位看观,在上一次的连载中,我们介绍了什么是时序电路,时序分析的两种分类(同步和异步),并讲述了一些关于SDRAM 的基本概念。这一次的连载中,我们将介绍什么是定时问题,怎样保证接收端的建立和保持时间。 信号经过传输线到达接收端之后,必须满足建立时间和保持时间这两个时序参数,它们由接收器本身的特性决定,可以 ..

[查看全文]

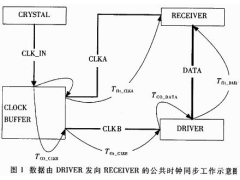

高速PCB设计中的时序分析及仿真策略

2012-12-25

秦洪密 李军

30

写在前面: 由于不是每个项目要求时间精度达到ns级,因此做同步电路的时候可以忽略很多设计因素.但是导致同步电路出现故障的原因,却大都是没有考虑同步电路的典型 特性和规则.作为新手,如果想从初步设计开始向进阶迈进,推荐阅读以下的文字.文章也许不一定100%正确,但是值得细细推敲和消化,有耐心的应该能有收获. 硕士博士可以 ..

[查看全文]

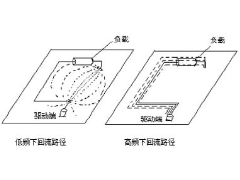

高速PCB设计中的一些问题

2012-12-21

23

随着器件工作频率越来越高,高速PCB设计所面临的信号完整性等问题成为传统设计的一个瓶颈,工程师在设计出完整的解决方案上面临越来越大的挑战。尽管有关的高速仿真工具和互连工具可以帮助设计师解决部分难题,但高速PCB设计也更需要经验的不断积累及业界间的深入交流。布线拓扑对信号完整性的影响当信号在高速PCB板上沿传 ..

[查看全文]

高速PCB设计的叠层问题

2012-12-20

Ming

11

随着高速电路的不断涌现,PCB板的复杂度也越来越高,为了避免电气因素的干扰,信号层和电源层必须分离,所以就牵涉到多层PCB的设计。在多层板的设计中,对于叠层的安排显得尤为重要。一个好的叠层设计方案将会大大减小EMI及串扰的影响,在下面的讨论中,我们将具体分析叠层设计如何影响高速电路的电气性能。 一.多层板和铺 ..

[查看全文]

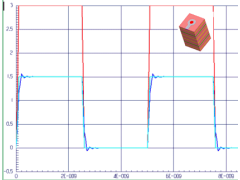

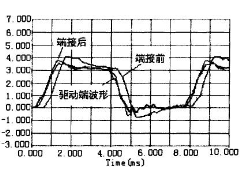

高速PCB过孔的影响以及时域分析波形图

2012-12-10

poqi055

20

此过孔在在设计阻抗为50欧姆、8层PCB板(FR4)上做的,信号是从顶层到底层。 使用Ansof的工具,计算的集总参数是: 电容: 0.68 pF 直流电阻: 5.2 毫欧姆 直流电感: 1.36 nH 交流电阻: 18.5 毫欧姆 交流电感: 1.09 nH 图中是时域波形分析,浅蓝色曲线是没有通过过孔的输出波形,深蓝色曲线是通过过孔的输出波形。 红色是输入波 ..

[查看全文]

高速PCB设计中的串扰分析与控制

2012-12-09

18

物理分析与验证对于确保复杂、高速PCB板级和系统级设计的成功起到越来越关键的作用。本文将介绍在信号完整性分析中抑制和改善信号串扰的方法,以及电气规则驱动的高速PCB布线技术实现信号串扰控制的设计策略。当前,日渐精细的半导体工艺使得晶体管尺寸越来越小,因而器件的信号跳变沿也就越来越快,从而导致高速数字电路系 ..

[查看全文]

基于PADS2004的高速PCB设计

2012-11-19

李琳

17

1 引言 随着IC工艺的提高,从几百兆赫到几千兆赫的处理器已经非常普及,以往的低速PCB设计方法已完全不能满足日益增长信息化发展的需要.利用EDA工具分析解决高速设计所而临的问题是一种有效办法。在设计的过程中,由EDA工具对输入器件模型数据进行分析,将结果直接反给设计者,设计者根据反馈信息对设计进行修改完善.从而缩 ..

[查看全文]

高速PCB板设计中的串扰问题和抑制方法

2012-10-26

曾铮

13

在当今飞速发展的电子设计领域,高速化和小型化已经成为设计的必然趋势。与此同时,信号频率的提高、电路板的尺寸变小、布线密度加大、板层数增多而导致的层间厚度减小等因素,则会引起各种信号完整性问题。因此,在进行高速板级设计的时候就必须考虑到信号完整性问题,掌握信号完整性理论,进而指导和验证高速PCB的设计。在 ..

[查看全文]

高速PCB理论综合测试题

2012-10-26

18

综合测试题 答卷人:得分:折合:55% 一. 封装知识考核(7分) (1)请阐明BGA封装为什么比DIP封装先进.(2分) (2)CSP封装的全称是什么?(2分) (3)CSP封装比其他封装更为先进的地方表现在那些方面?(3分) 二. 下图为PCB板上的一条内存地址总线电路. 给出条件: 1.图中n=8,其中L1=L2=…=L8=1 inch;图中的传输线长度只考虑此8 ..

[查看全文]

推荐文章

最新文章

热门文章