用Verilog-HDL做CPLD设计(组合逻辑电路的实现)

2012-06-02

李媛媛 常晓明

9

Verilog-HDL与CPLD/FPGA设计应用讲座 第 7 讲 用Verilog-HDL做CPLD设计 组合逻辑电路的实现 7.1 与非门的实现 7.2 2-1数据选择器的实现 7.3 2位二进制编码器的实现 7.4 1位数据比较器的实现 本讲中,我们通过由浅入深的实例来介绍组合逻辑电路在目标板上是如何实现的。 7.1 与非门的实现 首先,来实现一个用两个开关控制一个灯的 ..

[查看全文]

Verilog Pli的基本使用方法(modelsim)

2012-06-02

17

内容未做证实,仅供参考。 1.hello.c文件内容 #include #include "veriuser.h" static PLI_INT32 hello() { printf("Hi there\n"); return 0; } s_tfcell veriusertfs[] = { {usertask, 0, 0, 0, hello, 0, "$hello"}, {0} /* last entry must be 0 */ }; 2.hello.v文件内容 module hello; initial begin $hello ..

[查看全文]

Verilog脉冲发生器程序

2012-06-02

万雪松

24

/*************************************************************************************** 实现功能简述 本模块主要功能是产生一个确定时钟周期长度(最长为256个时钟周期)的脉冲信号,可以自己设定脉冲长度,输出的脉冲信号与时钟上升沿同步 脉冲宽度 = pulsewide + 1 时钟周期; 输入一个启动信号后,可以产生一个 ..

[查看全文]

锁存器 vhdl源程序

2012-06-02

9

锁存器 vhdl Library IEEE ; use IEEE.std_logic_1164.all ; ENTITY latchinf IS PORT ( enable, data : IN BIT; q : OUT BIT ); END latchinf; ARCHITECTURE maxpld OF latchinf IS BEGIN latch : PROCESS (enable, data) BEGIN IF (enable = '1') THEN q END IF; END PROCESS latch; END maxpld;

[查看全文]

VHDL设计举例:步进电机控制器

2012-06-02

24

LIBRARY IEEE; USE IEEE.std_logic_1164.ALL; USE IEEE.std_logic_unsigned.ALL; USE IEEE.std_logic_arith.ALL; ENTITY step_motor IS PORT( f, p, d: INSTD_LOGIC:='0'; speed : inSTD_LOGIC_VECTOR(1 downto 0); coil : OUTSTD_LOGIC_VECTOR(3 downto 0) ); END step_motor; ARCHITECTURE behavior OF s ..

[查看全文]

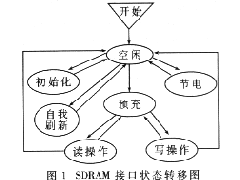

SDRAM接口的VHDL设计

2012-06-02

沙燕萍 曾烈光

21

SDRAM接口的VHDL设计 RAM(随机存取存储器?犑且恢衷诘缱酉低持杏τ霉惴旱钠骷?,通常用于数据和程序的缓存。随着半导体工业的发展,RAM获得了飞速的发展,从RAM、DRAM(Dynamic RAM,即动态RAM)发展到SDRAM(Synchronous Dynamic RAM,即同步动态RAM),RAM的容量越来越大、速度越来越高,可以说存储器的容 ..

[查看全文]

提高NC-Verilog仿真效率的技巧

2012-06-02

13

本文回顾了一些NC-Verilog的命令行选项,并说明这些选项如何影响仿真效率。同时,我们也展示了一些技巧,以帮助用户的NC-Verilog在最大效率下仿真一个设计和测试平台。 文中的命令行选项语法采用单步启动的方式(ncverilog +),这些选项也适合多步启动模式(ncvlog, ncelab, 或ncsim)。 安装最新发布的软件 首先确认你是否安 ..

[查看全文]

一个简单的总线轮询仲裁器Verilog代码

2012-06-02

17

下面这个是以输入信号作为状态机的转移条件,写得比较冗余: // // Verilog Module demo1_lib.bus_arbitor.arch_name // // Created: //by - Newhand //in - Shanghai ZhangJiang //at - 20:39:41 2003-12-03 // using Mentor Graphics HDL Designer(TM) // ///////////////////////////////////////////////////////// ..

[查看全文]

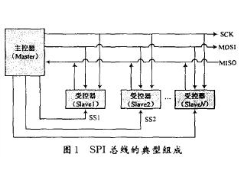

SPI串行总线接口的Verilog实现

2012-06-02

孙丰军 余春暄

16

摘 要:集成电路设计越来越向系统级的方向发展,并且越来越强调模块化的设计。SPI(Serial Peripheral Bus)总线是Motorola公司提出的一个同步串行外设接口,容许CPU 与各种外围接口器件以串行方式进行通信、交换信息。本文简述了SPI总线的特点,介绍了其4条信号线,SPI串行总线接口的典型应用。重点描述了SPI串行总线接口在一款 ..

[查看全文]

推荐文章

最新文章

热门文章