异步FIFO的VHDL设计

2013-04-06

10

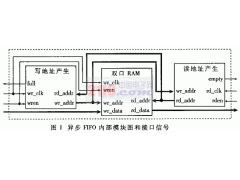

FIFO(先进先出队列)是一种在电子系统得到广泛应用的器件,通常用于数据的缓存和用于容纳异步信号的频率或相位的差异。FIFO的实现通常是利用双口RAM和读写地址产生模块来实现的。FIFO的接口信号包括异步的写时钟(wr_clk)和读时钟(rd_clk)、与写时钟同步的写有效(wren)和写数据(wr_data)、与读时钟同步的读有 ..

[查看全文]

在FPGA中基于信元的FIFO设计方法

2013-03-30

13

设计工程师通常在FPGA上实现FIFO(先进先出寄存器)的时候,都会使用由芯片提供商所提供的FIFO。但是,由于其通用性使得其针对性变差,某些情况下会变得不方便或者将增加硬件成本。此时,需要进行自行FIFO设计。本文提供了一种基于信元的FIFO设计方法以供设计者在适当的时候选用。这种方法也适合于不定长包的处理。 FIFO在 ..

[查看全文]

单片机和 FIFO 的接口汇编程序

2013-03-23

21

下面的程序中,单片机将FIFO中的数据读取出来后,从串口发送出去。 ;*********************************** ef bit p3.3 ;fifo empty flag rst bit p3.5 ;reset fifo read bit p3.7 ;read fifo org 0000h ljmp main org 0030h main: ;------ initial timer mov tmod,#00100001b ;time ..

[查看全文]

非对称同步FIFO的设计

2013-02-06

5

本文在分析了非对称同步FIFO的结构特点及其设计难点的基础上,采用VHDL描述语言,并结合FPGA,实现了一种非对称同步FIFO的设计。 引言 FIFO是一种常用于数据缓存的电路器件,可应用于包括高速数据采集、多处理器接口和通信中的高速缓冲等各种领域。然而在某些应用,例如在某数据采集和处理系统中,需要通过同步FIFO来连接 ..

[查看全文]

基于Verilog HDL语言的32X8 FIFO设计

2012-12-24

夏传红 王祖强 李秀娟

12

摘要:介绍了FIFO的基本概念、设计方法和步骤,采用了一种新颖的读、写地址寄存器和双体存储器的交替读、写机制,实现了FIFO的基本功能,同时使本32X8 FIFO拥有可同时读、写的能力,完全基于Verilog HDL语言实现了电路功能并应用Synopsys公司的DesignCompiler和VCS对其进行综合、仿真。 对基于单体存储器的FIFO,作为一种数据 ..

[查看全文]

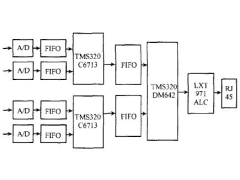

基于TMS320C6000 DSP的FIFO-网络数据传输

2012-12-19

梁迅 熊水东 姚琼

19

网络技术在飞速的发展,网络接口的性能也在不断提高。由于以太网接口成本低,速度快,性能好,开发方便,越来越多的数据采集系统采用以太网接口作为最终的数据输出及控制端口。而在相应的嵌入式系统领域,越来越多的芯片,从单片机到DSP,也都逐渐开始支持以太网接口。TCP/IP协议是被广泛支持的以太网协议,在嵌入式系统中 ..

[查看全文]

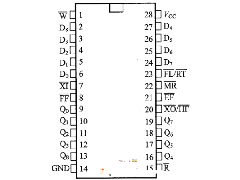

实际的FIFO存储器

2012-10-02

15

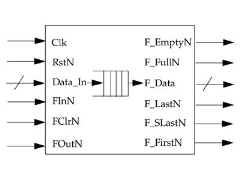

作为实际的FIFO存储器,我们以Cypress公司的CY7C419为例进行说明。CY7C419是L0b字×9位结构的FIFO存储器,其引脚配置如图1所示。在与CY7C419相同的系列中,还包括内部结构为512字×9位(CY7C421)以及1K字×9位、2K字×9位、4K字×9位(分别为CY7C425/429/433)的产品。由于FIFO存储器没有地址引脚,因而 ..

[查看全文]

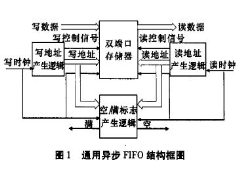

一种基于格雷码的异步FIFO设计与实现

2012-06-26

吴昆 黄坤

58

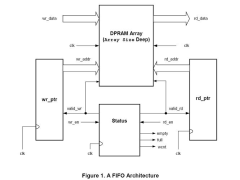

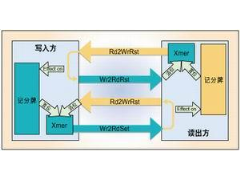

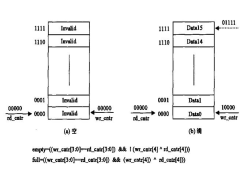

1 引言 FIFO(First IN First Out)先进先出电路是一种实现数据先进先出的存储器件,普遍用作数据缓冲器。FIFO的基本单元是寄存器,作为存储器件,FIFO的存储能力是由其内部定义的存储寄存器的数量决定。 FIFO通常是双端口的存储器,其中一个端口用于写入数据,而另一个端口用于读出数据。可以同时对存储器字存储单元进行写入和 ..

[查看全文]

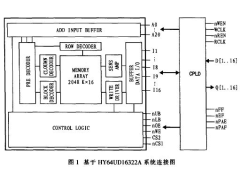

基于SRAM和DRAM结构的大容量FIFO的设计与实现

2012-06-25

杨奇 杨莹

12

1 引言 FIFO(First In First Out)是一种具有先进先出存储功能的部件,在高速数字系统当中通常用作数据缓存。在高速数据采集、传输和实时显示控制领域中,往往需要对大量数据进行快速存储和读取,而这种先进先出的结构特点很好地适应了这些要求,是传统RAM无法达到的。 许多系统都需要大容量FIFO作为缓存,但是由于成本和容量 ..

[查看全文]

可综合的Verilog FIFO存储器

2012-06-02

12

可综合的Verilog FIFO存储器 This example describes a synthesizable implementation of a FIFO. The FIFO depth and FIFO width in bits can be modified by simply changing the value of two parameters, `FWIDTH and `FDEPTH. For this example, the FIFO depth is 4 and the FIFO width is 32 bits. The input/output p ..

[查看全文]

推荐文章

最新文章

热门文章