嵌入式系统设计师考试笔记之嵌入式系统基础知识

2012-06-02

欧浩源

10

一、引言 自《嵌入式系统设计师考试复习笔记之存储管理篇》在嵌入式在线的博客出现后,意外的得到很多朋友的关注和评论,收到不少朋友的邮件,问一些有关考试的问题,希望得到我的复习笔记的其他部分。我非常感谢他们,他们的热切关注,使我有了继续往下写的无限动力,使我萌生了将我以前的复习笔记、考试经验结合大纲教程并 ..

[查看全文]

自己动手打造嵌入式Linux软硬件开发环境

2012-06-02

dai lizhou

9

Linux和uClinux 1991年8月,芬兰的一个学生在comp.os.minix新闻组贴上了以下这段话: 你好所有使用minix的人-我正在为386(486)AT做一个免费的操作系统(只是为了爱好,不会象gnu那样很大很专业. 这名学生就是Linus Torvalds, 而他所说的'爱好'就变成我们今天知道的Linux。 由于Linux的源代码公布在互联网上,可以免费得到, ..

[查看全文]

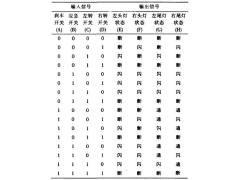

汽车车灯控制系统的VHDL语言实现

2012-06-02

郑应民

9

当前数字电路系统的设计正朝着速度快、容量大、体积小、重量轻的方向发展。利用大规模可编程逻辑器件CPLD(Complex Programmable Logic Device)进行ASIC设计,可以直接面向用户需求,根据对系统的功能要求自上而下地逐层完成相应的描述、综合、优化、仿真与验证,直到生成元器件。目前,系统级的仿真工具也已出现.这样可以大 ..

[查看全文]

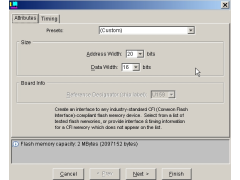

Nios II中Flash的使用

2012-06-02

10

在嵌入式系统中,Flash是最常用组件之一。许多使用过flash的朋友都了解,Flash的特点是“读来容易写来难”。通常,可以直接读出Flash的内容;但如果要写入数据,就要发送一长串命令,比如像:555 ,AA,2AA,55,555,A0 ,PA,PD就表示对PA地址写入数据PD,实际情况还要复杂一点,因为通常还要包含许多查询 ..

[查看全文]

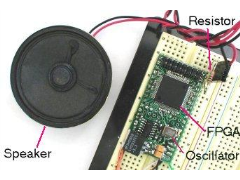

FPGA播放声音和音乐

2012-06-02

43

这里我们将让我们的FPGA播放声音和音乐。我们从产生一个单频音开始。然后,逐步让它实现一些更加有趣的功能,例如播放警笛和曲子。 这个工程中用到的硬件器件包括:一块Pluto板、一个扬声器(speaker)以及一个1千欧姆的电阻(resistor)。 关于此硬件系统的一个更加正式的表示方法如下图所示: 振荡器(oscillator)产生一个固定频 ..

[查看全文]

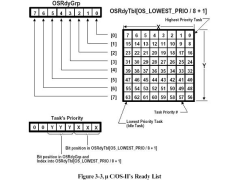

uCOS II就绪表(Ready List)分析

2012-06-02

19

3.0 就绪表(Ready List) 每个任务被赋予不同的优先级等级,从0级到最低优先级OS_LOWEST_PR1O,包括0和OS_LOWEST_PR1O在内(见文件OS_CFG.H)。当uCOS II初始化的时候,最低优先级OS_LOWEST_PR1O总是被赋给空闲任务idle task。注意,最多任务数目OS_MAX_TASKS和最低优先级数是没有关系的。用户应用程序可以 ..

[查看全文]

FPGA等效门数的计算方法

2012-06-02

20

1. 把FPGA 基本单元(如LUT+FF,ESB/BRAM)和实现相同功能的标准门阵列比较,门阵列中包含的门数即为该FPGA 基本单元的等效门数,然后乘以基本单元的数目就可以得到FPGA 门数估计值; 2. 分别用FPGA 和标准门阵列实现相同的功能,从中统计出FPGA 的等效门数,这种方法比较多的依赖于经验数据。 对于第一种方法,FPGA ..

[查看全文]

半整数分频的VHDL程序

2012-06-02

10

想出了一个半整数分频的VHDL语言描述 其实很多问题只要你耐心,也是比较容易的 写出来与大家共享,共同讨论,半整数分频当然还有其他的方法 我认为这种看起来蛮简单的 library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity abc is port(clk:in std_logic; dout:out std_logic); end abc; architecture x ..

[查看全文]

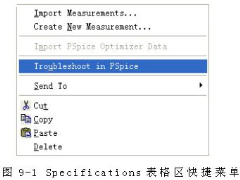

从实例中学习OrCAD-PSpice 10.3-AA(第9章 仿真的故障排除)

2012-06-02

48

第9章 仿真的故障排除 在运行高级分析工具的过程中,由于操作失误、参数设置不合理等方面的原因,常常出现错误信息或者系统仿真不能运行等情况,用户往往得不到理想的分析结果,面对这些存在的难题,不能坐着发闷,要积极的解决问题。本章主要介绍运用故障排除分析工具解决存在问题的使用方法及高级分析中一般性故障的解决方 ..

[查看全文]

基于VxWorks的一种程序倒换解决方案

2012-06-02

殷智刚 马宏 高志强

16

摘要:VxWorks嵌入式系统广泛应用于通信领域,程序倒换是软件设计中的重要内容。结合VxWorks的特点,本文提出了一种简单有效的解决程序倒换的方法,该方法在七号信令的单板程序中得到很好的应用。 0 引言 VxWorks是美国WindRiver公司的产品,它是一个运行在目标机上的高性能、可裁减的嵌入式实时操作系统,自上世纪八十年 ..

[查看全文]

利用ModelSim SE6.0C实现时序仿真

2012-06-02

16

1) 打开一个工程文件。 2) 打开Settings设置栏,选择EDA Tools Settings下的Simulation栏。在右边出现的设置栏中将“Tool name”的下拉菜单选择“ModelSim(Verilog)”(如果工程用VHDL语言实现,则可以选择“ModelSim(VHDL)”;如果ModelSim使用的是for Altera的专用版本,则可以选择 ..

[查看全文]

VXWORKS内核分析

2012-06-02

18

1. 实时操作系统的结构 在计算的早期开发的操作系统的最原始的结构形式是一个统一的实体(monolithic)。在这样的系统中,提供的不同功能的模块,如处理器管理、内存管理、输入输出等,通常是独立的。然而他们在执行过程中并不考虑其他正在使用中的模块,各个模块都以相同的时间粒度运行。 由于现代实时环境需要许多不同的功能, ..

[查看全文]

推荐文章

-

热敏电阻温度阻值查询程序2024年11月13日 109

-

C99语法规则2024年11月16日 1011

-

FreeRTOS 动态内存管理2024年11月12日 484

-

一款常用buffer程序2024年11月06日 121

-

1602液晶显示模块的应用2012年08月03日 203

-

GNU C 9条扩展语法2024年11月18日 300

最新文章

-

Corext-M3中断的具体行为2025年11月11日 66

-

优秀的字符串哈希算法-ELFhash2024年11月26日 110

-

SD卡TF卡引脚定义2024年11月26日 105

-

C语言string.h常用函数重点说明2024年11月22日 62

-

C语言下划线命名法2024年11月22日 74

-

C数组 结构体 联合体快速初始化2024年11月22日 60

热门文章

-

C99语法规则2024年11月16日 1011

-

51单片机LED16*16点阵滚动显示2012年09月05日 672

-

FreeRTOS 动态内存管理2024年11月12日 484

-

ARM9远程图像无线监控系统2012年07月03日 435

-

用单片机模拟2272软件解码2012年09月06日 311

-

如何实现STM32F407单片机的ADC转换2024年11月15日 310