PART 6:

1,ALLEGRO中直接从库中调的元件不能定义网络及 Ref des。

(是的。这样一来可以保证你LAYOUT结果和原理图目的是一致的,而不会因为不小心而出错。一般我们不应该直接从库中调元件,而应通过导入新的NETLIST 来增加新元件.)

2,ALLEGRO中只能 UNDO一次,简直不能容忍。

(15.0版本将增多步Undo、Redo功能)

3,公英制转换偏差太大。

(由于计算精度的限制,公英制的来回转换会产生一定的累积误差,因此在设计过程中,应尽量避免频繁转换公英制)

4,Toolbar的功能描述没有。Toolbar 随意添减图标易出错。

(在下面版本中,Allegro将会有Toolbar的功能描述。你可以先选择Defaults,然后部分改变toolbar,但是只要是正常操作,Toolbar 的添减是不会出错的)

5,差分信号线调成圆弧线段很困难。

(可能是靠里面的线半径设的过大了)

6,对于颜色的设置不能EXPORT颜色文件,每块PCB都必须重新设置颜色。

(Allegro没有保存颜色表的功能,但是可以通过其他简单的方法解决,如:调用Script功能;或着准备一个空板,里面只保存偏好的颜色设置,把网表Export到这个空板就可以了)

8,Allegro里没有对齐元件的功能。

(后面版本的Allegro将会有对齐功能)

9,选择元件或Trace时,不能如 CONCEPT HDL添加漏选的东西或者不能去除多选的东西,也就是说,在板内划出矩形选择框,框到啥就是啥,框到不想选的东西,那也得承受,没有框到要选择的东西,那也没办法。

(如果选择零散目标的话,可以使用Temp Group功能,例如:Move->右键-> Temp Group->点选->Complete)

10,垃圾文件太多,不知那些有用。

(Cadence 实际上极少产生垃圾文件,许多文件都是设计高速PCB所需要的。每个文件的作用可以参考培训手册)

11,Allegro布线时,相同的网络和Trace为什么不能都高亮显示?

(14.1 以后版本已解决)

12,Allegro步线抓焊盘的功能太弱,不能保证线段结束时连接在PIN的中心。

(在Allegro右面的Control panel->Option中选择:Snap to connect point,并请在布线时连到Pad前,右键选TOGGLE即可。如经常性出现此问题,可将 TOGGLE设成快捷键方式)

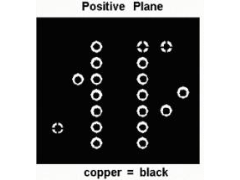

13,编辑Shape 时,选择Boundary还得十分小心,有一点重合都不行。

(可以通过调整GRID来修改铜箔,这样一来更容易)

14.CCT 布线时网络不高亮;由 ALLEGRO 到 CCT 前布的线只能删除,不能回退,不能自动优化鼠线.

15.ALLEGRO:鼠线不能只显示当前屏幕上的PIN的鼠线,全屏布线时高亮不明显.

(方法一:可以在setup->user preference->display中,勾选display_nohilitefont项,将高亮设为实线显示;

方法二:改变高亮颜色。点击Hilight 按钮,右面控制面板的Option 栏会提供可选择的颜色表;

方法三:使用Shadow Mode,明暗的对比度可以在Color and Visibility中的Shadow Mode 项调整。)

三种方法配合使用,会得到更好的显示效果。

16.在ALLEGRO中,改变线宽时鼠标需放在线宽栏的右边才可改变。

(使用时光标应在Control Panel区域,一旦移到 Work area 就开始执行Allegro命令,因此就不能再进行输入,不过这个问题是可以改进的)

17.放置器件时,不能在原理图里同时选多个元件拖放到PCB里(布局时).

(14.1 就可以。在ConceptHDL 中按住Shift 键多选,然后在Allegro里便可依次放置)

18.布局不能优化网络,飞线以最近连接显示,而不是最佳显示方式(没有动态连接功能)。

(Cadence 注重约束驱动布线,因此不会有飞线的动态连接)

19.在 ALLEGRO 中没有网络也可以走出一根走线.(很容易造成多余的线头)并且清除线头及多余过孔也不彻底!(GLOSS命令)

(如何去掉断线头?分为有网络属性的断线头和VIA,同无网络属性的断线头两种。

对无net 的断线头,可以通过Hilight 来实现,要把Hilight 的Color 同client相区别。可多试几试hilight 的color 来发现断线头。

对有net 属性的断线头和VIA(如图二),可采用:

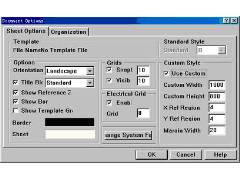

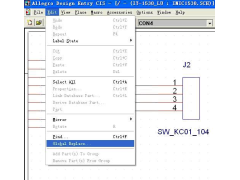

在 ROUTE/GLOSS/PARAMETER 下,选中 1,2,3 项,点选 GLOSS 即可(如下图):

点击左边的方按钮,还可以改变参数的设定。

20.14.0 的原理图到 14。1 的 PCB 转网表时在空板时可以转入,但是后来网表变化,不能转进来 (报错:NET NAME ALREADY EXIST),有时换一台机器即可,随机性很大!

(此问题已解决,请安装最新的补丁盘或到下面地址下载补丁程序、安装:

ftp://ftp.cadence.com/patches/PSD141/allegro/algroF2B14.10-s018wint.exe

ftp://ftp.cadence.com/patches/PSD141/allegro/algroBase14.10-s056wint.exe )

21.铜箔及差分线倒圆弧非常不方便,没有直接的命令可以在走完90或45度角后,方便倒圆弧(最好能像CADSTAR拉圆弧)

(我们会把此问题报告到Cadence R&D,希望尽快解决)

22.ALLEGRO中最好可以方便走排线。

(CCT 具备此功能。Allegro走排线功能正在开发中)

23.14.0做库,库sym字符在原理图中可以随便移动

(14.1 版本已解决)

24.14.0做库,在14.1原理图中sym旋转,而字符不随着旋转(如:电解电容的“+“号)

(14.1最新的补丁盘已解决此问题)

25 14.0原理图中的sym如果 mirror,转到14.1看元件并未 mirror

(14.1最新的补丁盘已解决此问题)

26.做库时,用HDL 编辑完元件,如果回到 PART DEVELOPMENT 存盘,就会将刚改完的元件回复成未改前的图形。

(即将发布的14.2版本已解决此问题)

27.用Net logic 改变的网络不能反标至原理图

(可以。用tool2->design association可以反标网络)

28.Allegro 关于 area 的规则不能完全带入 CCT,即只能带入 region 规则,不能带入region class 等比region优先级更高的规则

29.14.1 CCT内有些线在没有对其进行任何操作的情况下,有时候会莫明其妙的变到另一层中 (有时从CCT回到ALLEGRO,会发现本来在 BOTTOM 层的变成 TOP层)

(最好能提供一个可以重复出现此问题的例子,以便查找原因)

30.Allegro 和 CCT 都没有 snap 的功能,即当直线至目标 PIN 附近时,会自动吸附到 PIN 的中心。BGA 布线时,由于 PIN 间允许走线的范围很小,要把鼠标位置定得很精确才能拉出一根线,实际操作很费劲。如果有 snap 功能的话,就可以允许有一定的裕度,如 8mils,即当鼠标左右偏移小于 4mils 且偏移位置不允许布线时,route 应停留得最接近该位置的允许布线区

(Allegro 和CCT都有snap功能)

31.Allegro没有BUS 走线的功能,差分线不能同时布线

(目前走BUS线可以到 CCT里完成。从PSD14.2 开始,Allegro对差分线的处理功能将会大大加强)

32.CCT 差分线布线困难,经常不能转弯,而且有时候想单独处理其中一根线时不被允许

(这种情况可在ALLEGRO中处理,15.0将会对此做较大改进)

33.CCT同时走多根线可差分线时不允许two-seg方式,以不能精确定位

(同上)

34.CCT的two-seg布线方式和Allegro布线时要不断功换toggle 功能,非常不方便,应让软件自动识别。

(同上)

35. 14.1CCT 中鼠标中键的功能经常莫名其妙地丢失

(可在命令行中键入” bind_mouse_button M zoom_pan”来恢复.)

36.布线时设定过孔,无法用预缆方式,只能自己去了解过孔名,然后自己敲名字。

(这的确是一个缺点。该问题已列入15.0改进计划)

37.在allegro里推动过孔时有可能会冒出一大堆错,还不能undo.

(14.2对过孔的推挤有很大改进)

38.有时优化走线时,旧线还需要再手动删除。

(优化走线是在原走线的基础上进行,因此不会有新线产生)

39.电源地线进到cct时容易掉线。

(最好能提供一个可以重复出现此问题的例子,以便查找原因)

40.设定最小线长与最大线长,当线长小于设定时,没有 DRC 报错(ELECTRICAL CONSTRAINT SPREATSHEET)

(在 14.0 版本以后,Allegro 增加了未布线的最小线长检查,可以通过对环境变量CHECK_MIN_DELAYS 的设置来实现,如果设置为 ON的话,当线长小于设定时,将会有DRC报错。其检查的依据是两个PIN之间飞线的曼哈顿距离)

41.13.6做的原理图,转到14.1不能将数据传递给已经UPREV 的原13.6的板.

(问题提的不很清楚。从14.0开始:

1、因为添了约束管理器,不能从高版本的向低版本传递数据;

2、uprev13.6的板时Flash symbol 也需要uprev,勾选use preference中 Misc里面的old_style_flash_symbols 即可;也可以使用批处理转换,DOS命令:

FOR%%fIN(*.bsm)DOflash_convert%%f

3、如果跟约束有关,要注意原来的DELAY_RULE和MATCHED_DELAY 已改为 PROPAGATION_DELAY和RELATIVE_PROPAGATION_DELAY)

42. ALLEGRO中UPDATE SYMBOLS 时,LIBRARY中的该元件明明已改过来,但就是不能UPDATE过来,并且从PACKAGE SYMBOL中也看不到该器件(不选DATA BASE,就选LIBRARY)

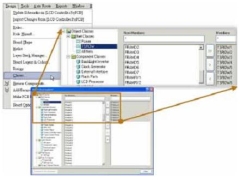

(应该是路径方面的问题,不然 Package Symbol 里不会看不到的,请仔细检查一下环境变量的设置。或者你可以这么试试,在 Concept 里重新以 Phisical方式Add 这个器件,然后Export(用Update Allegro Board 并且勾选 ECO)

附注:如果用户对以上解答内容不理解、经过测试仍未解决问题或还有其他更多的问题,请及时与Cadence当地工程师联系:

-

怎样设计一块好的PCB板2012年07月28日 59

-

高速PCB设计指南(三)2013年03月27日 140

-

PCB布线设计(二)2013年03月23日 38

-

混合信号PCB的分区设计2013年03月04日 23

-

高速PCB设计指南(六)2012年12月29日 25

-

PCB布线设计(一)2012年10月22日 13

-

高速PCB设计指南(五)2012年10月15日 15

-

电气安全距离要求及分类2012年09月06日 273

-

PROTEL 99SE的打印设置2013年02月08日 381

-

Protel dxp等长走线2013年01月02日 329

-

Cadence 中添加工艺库文件步骤2013年01月16日 280

-

电气安全距离要求及分类2012年09月06日 273

-

在ORCAD中整体修改网络名称2012年07月26日 173

-

Allegro铺铜的学习2012年12月05日 171

-

Altium Designer焊盘为梅花状连接,过孔为直接连接的方法2013年01月25日 159

-

差分信号线的分析和LAYOUT2012年09月16日 144