1:LVDS器件简介

对于高速电路,尤其是高速数据总线,常用的器件一般有:ECL、BTL、GTL和GTL+等。这些器件的工艺成熟,应用也较为广泛,但都存在一个共同的弱点,即功耗大,此外,采用单端信号的BTL和GTL器件,电磁辐射也较强。现在,NS公司率先推出的CMOS工艺的低电压差分信号器件(即Low Voltage Differencial Signal 简称LVDS )给了我们另一种选择。

LVDS器件是近年来National Semiconductor公司发展的一种高速传输芯片,它的传输机制是把TTL逻辑电平转换成低电压差分信号,以便于高速传输。与传统的ECL逻辑相比,它采用CMOS工艺,它的电压摆幅更低,只有400mv,ECL为800mv,动态功耗更小,(输出电流3-5mA)只有ECL电路的1/7(相同的数据传输量),低EMI,价格更低,因而具有很大的优势,从97-98年首先在欧洲开始得到应用。目前,NS公司的LVDS器件有以下几个系列:

- Channel Link,如:DS90CR285/6,DS90CR217/218

- Bus LVDS,如:DS92LV1021/1201

- Flat Panel Display (FPD)- link,如:DS90CF385/386

- Line Drive and Receiver (LD&Rs),如:DS90LV031A/032A

LVDS器件的推出时间不长,目前,已经在欧美地区开始应用,据了解,国内目前尚没有应用,但已有几家公司在进行测试和试用。现有的LVDS器件单对差分线所能传输的最大速率为400-600M左右,据悉NS公司正在开发速率为1G的芯片组。其它公司,如TI、朗讯,都有各自的LVDS类型的芯片。3M公司则开发了LVDS信号专用的双绞电缆和接插件。LVDS器件主要用途为:电缆或PCB传输(点对点)、总线传输(BLVDS)、平板显示器(FPD)等,传输速率在400M-600M,今后的LVDS器件的速度将会提高到1G,速度越来越快,品种也会越来越多。

据目前掌握的资料,未来几年,NS将推出单对差分线传输速率达千兆位的LVDS收发器、低延迟的LVDS时钟信号缓冲器/驱动器,以及36X36LVDS信号的SWITCH芯片。另外,Ericsson 和Sony 公司已经推出传输速率超过1G的GLVDS器件。

2:LVDS器件的标准

2.1:ANSI/TIA/EIA-644

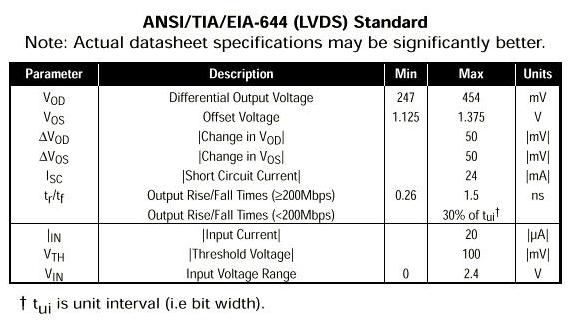

ANSI/TIA/EIA-644是由TR30.2制定的,这个标准定义了收发器的输入输出阻抗,但是这仅仅是一个电气特性标准。其并不包括功能性和协议规格,完全是应用独立的。ANSI/TIA/EIA-644打算通过使用别的协议来完善 整个接口功能。这使的这个标准在很多方面便于实现。在标准中推荐的最大操作速率是655Mbps,理论最大使用速率是1.923Gbps。传输速率与使用的介质损耗有关。这个标准同时也说明了最低的介质要求、收端的fail-safe电路、多路操作等。标准见下表:

表1:ANSI/TIA的LVDS标准

2.2:IEEE 1596.3 SCI-LVDS

SCI-LVDS被定义作为SCI的一个子集,在IEEE 1596.3中有详细说明。SCI-LVDS说明了应用于高速/低功耗物理接口的电气规范,同时也定义了用于SCI数据传输的包交换的编码格式。SCI-LVDS在特定的条件下也支持高速的RAMLINK传输。SCI-LVDS同TIA除了在一些电气要求和负载条件有差别,在别的方面十分相似。两个标准支持相似的驱动输出电平,接收门限电平,数据传输速率。在两个标准中TIA的应用更为普遍,同时TIA也支持多负载情况。

3:LVDS器件的工作原理

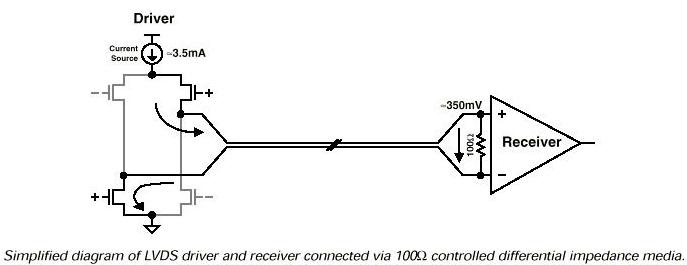

LVDS器件的工作原理如下图所示:

其中发送端是一个约为3.5mA的电流源,产生的3.5mA的电流通过差分线的其中一路到接收端。接收端对于直流表现为高阻,电流通过接收端的100欧姆的匹配电阻产生350mA的电压,同时电流经过差分线的另一条流回发送端。当发送端进行状态变化是它通过改变流经电阻的电流的方向产生有效的’0’和’1’态。

4:LVDS的特点

LVDS的特点是电流驱动模式,低电压摆幅350mV可以提供更高的信号传输速率,使用差分传输的方式可以使信号的噪声和EMI都减少:

A、低的输出电压摆幅(350mV)

B、低的信号边缘变化率, dV/dt 0.350V/0.5ns = 0.7V/ns

C、差分特征是磁干扰相互抵销。

D、软的输出切换

E、最小的Icc切换电流变化。

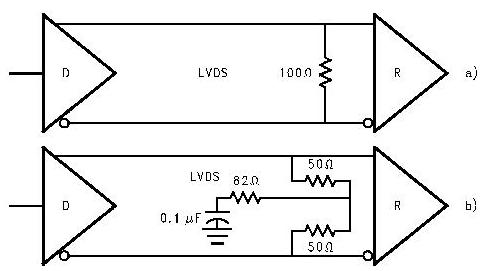

同时由于使用电流驱动模式,对LVDS电路的匹配方式极为简单,可以有以下两种方式

图3:LVDS接口信号的匹配图

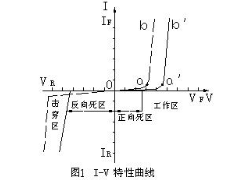

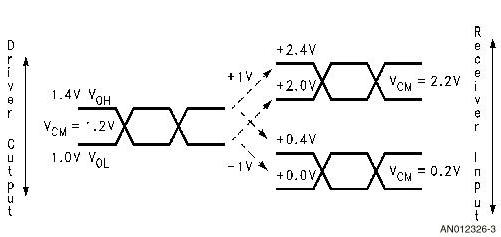

其中第一种方式最为简单,也最为实用。对第二种匹配方式对共模干扰有更好的抑制作用,但是因为差分信号本身的特点一般是没有必要的,这种匹配方式对PCB设计是的布线的难度加大,这对于高密度的PCB板的设计是不利的。对于LVDS的接收端一般可以忍受大范围的共模对地偏压。一般LVDS收端可以忍受+/-1V的在发端地和收端地之间的地漂移。LVDS的典型的驱动偏置是1.2V,加上可以承受的地漂移收端的偏置可以从0.2V到2.2V。推荐的收端输入电压范围是从地到2.4V。参见下图:

图4:LVDS的逻辑电平图

5:LVDS的设计

5.1:LVDS在PCB上的应用

LVDS在PCB的应用应该注意遵循以下准则:

- 对LVDS的使用,不论信号的数量多少,都建议使用多层板,最少四层设置,LVDS、GROUND、POWER、TTL。

- 对LVDS信号和其它信号比如TTL信号,最好能使用不同的走线层,如果因为设计限制必须使用同一层走线,LVDS和TTL的距离应该足够远,至少应该大于3~5倍差分线间距。

- 保证收发器到接插件的距离足够短,防止由于STUB线过长引起信号的崎变,一般要求距离小于10mm。

- 对收发器的电压和地使用滤波电容,滤波电容的位置应该尽量靠近电源和地管脚,滤波电容的值可以参照器件手册。

- 对电源和地管脚与参考平面的连接应该使用短和粗的连线连接。同时使用多点连接。

- 保证地电流回路短而粗。

- 对走线的阻抗要求进行控制,一般差分阻抗控制在100欧姆。匹配电阻的阻值可以进行调整。

- 对走线方式的选择没有限制,微带线和带状线均可,但是必须注意有良好的参考平面。对不同差分线之间的间距要求间隔不能太小,至少应该大于3~5倍差分线间距。

- 对接收端的匹配电阻到接收管脚的距离要尽量的靠近,一般应小于7mm,最大不能超过12mm。

- 未使用的管脚可以悬空。

5.2:LVDS在电缆中的使用

LVDS在电缆中的使用同在PCB中的使用方式并无大的差别,需要注意在不同电缆中LVDS差分信号需要不同的排布方式。

Ribbon Cable 不适合用作LVDS传输的介质,如果要使用应该保证地线同信号线间隔,电缆的长度尽可能短,信号的速率要尽可能低。屏蔽双绞线比较适合作为LVDS传输的介质,CAT3电缆可以传输5m,CAT5电缆可以传输更远距离的LVDS信号。

5.3:LVDS在接插件中的信号分布和应用

LVDS在接插件的信号的分布布不同造成的串扰的差别是很大的。但是有一点必须保证的是对于差分信号线的周围都必须有地针,也就是说对不同的信号线是不允许相邻排布的。下面的LVDS信号的排布可以说是一种比较好的排布方式,不但满足了上述的基本要求,同时接插件的利益率也很高。具体可参考下图对于实际的系统中应该使用怎样的信号排布,要遵循的主要原则是:

- 对称。在一对差分信号线中,两条信号线的路径要一致,要布置在相邻的PIN上。

- 信号线与地线的比例。稳妥的做法是保持信号地的比例为1:1,并且,用地线把信号线分离开。这样的比例可以保证信号回流路径的顺畅和信号间较低的串扰。

- 接插件的选择。这与系统的成本和对信号质量的要求有关。不同的接插件有不同的电气性能。目前,公司常用的接插件为2mm接插件,信号的速率在1.25Gbps的情况下,仍然能够保持很好的性能。在信号速率超过2G的情况下,建议采用HS-3接插件。

6:LVDS信号的测试

LVDS信号的测试应该使用宽带数字采样示波器和宽带高阻抗探头。

1,选择示波器的要求

首先,示波器的带宽应该满足被测试信号的带宽要求。LVDS信号的模拟带宽取决于信号的边沿时间,不等于信号的比特速率,一般都比信号的比特速率高的多。如622Mbps的信号的带宽可能高达1GHz。因此,选择示波器时需要注意信号的带宽要求。

2,探头的选择

由于LVDS信号是差分信号,因此,应该尽量采用差分探头,如TEK公司的P6247等。如果没有差分探头,可以考虑使用两个单端探头,如TEK公司的P6245等。对于在线测试,要求示波器的探头为高阻输入。并且,由于LVDS信号的速率一般比较高,示波器探头的寄生电容也应当选择比较低的型号。此外,还可以把示波器作为LVDS信号的负载的形式来测试。一般采用一对50欧姆同轴电缆把信号引入到示波器的输入端,同时,断开板上原有的负载。 在这种情况下,要求示波器要有50欧姆输入。同轴电缆的带宽一般都可以达到要求,不需要考虑带宽的影响。

3,测试方式

LVDS信号属于高速数字信号,可以采用眼图测试的方式来观察信号的质量。

7:LVDS器件应用举例

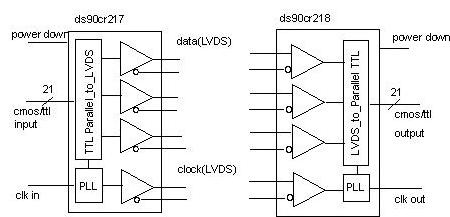

下面以DS90CR217/218为例对LVDS的器件应用加以说明。

图5: DS90CR217/218器件的原理图

时序要求:该芯片组内部有PLL,用于在发送端产生发送时钟,以及在接收端恢复时钟。在LVDS高速码流中,每一比特位的宽度为发送时钟周期的1/7。如果发送时钟为85M,周期就是11.76ns,那么,LVDS码流的比特位宽为1.68ns 。同一差分线对中两条线间的相位差、差分线对之间的相位差、以及时钟的抖动都会减小LVDS信号的采样窗口。因此,必须保证发送器的时钟抖动尽可能小,PLL的电源脚应单独处理,要有足够的去藕电容(要求0.1uF 、0.01uF 、0.001uF各一个)。此外,同一芯片上的差分信号线应严格等长,使差分线对之间、差分线对中的两条线间的相位差应尽量小,以便给接收端留出尽量多的采样余量。试验表明,在差分线的长度控制得较好的情况下,用2071ASL(jetter Max<300ps)或50ppm 的晶振是可以满足要求的。

上电时序及三态:在VCC电源电压到达2V之前,发送器的输出保持三态,当powerdown高于1.5V ,VCC到达3V后10ms,数据和时钟输出端开始有效。任何时刻,当Powerdown 端置低,100ns 后发送器三态;1us 后,接收器三态。任意时刻,发送器掉电后,接收器的输入/输出时钟将立即停止,同时,数据输出端将保持时钟停振时的状态。接收器掉电时,其输入端将由内部的一个二极管上拉到VCC。

-

一款高温报警电路2024年11月13日 81

-

可燃气体全自动点火器2012年09月22日 76

-

LED参数与特性2012年09月18日 118

-

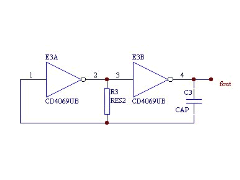

RC振荡电路的几种接法2012年09月10日 221

-

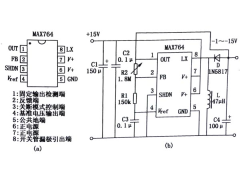

MAX764极性反转电路2012年08月24日 47

-

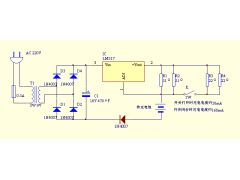

实用恒流充电器2012年08月18日 175

-

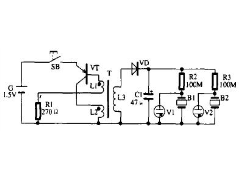

电子催眠器制作2012年08月15日 72

-

多普勒自动电子开关2012年08月02日 78

-

常用物质金属非金属的电阻率、导电率明细表2024年11月23日 4874

-

自制微型交流电焊机2012年07月14日 1143

-

声光控延时开关的制作2024年07月06日 915

-

用LM1875替找TDA20302012年09月15日 777

-

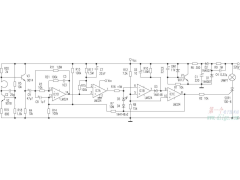

6N3+LM4780功放制作2012年09月13日 653

-

小型太阳能供电板的制作2012年09月08日 649

-

简单的逆变器电路2012年07月08日 560

-

1000米晶体稳频FM立体声发射机2012年07月22日 499