CPLD开发板和FPGA开发板的区别

2012-06-02

抽烟的鱼

19

市面上尤其是学校里面可以看到Xilinx公司或者Altera公司各种不同的开发板,其实只有两个大类,CPLD开发板和FPGA开发板。尽管FPGA和CPLD都是可编程ASIC器件,有很多共同特点,但由于CPLD和FPGA结构上的差异,具有各自的特点: ①CPLD更适合完成各种组合逻辑,FPGA更适合于完成时序逻辑。换句话说,FPGA更适合于触发器丰富 ..

[查看全文]

modelsim仿真问题

2012-06-02

86

近段时间比较忙,尝试着将工作中碰到的问题记录下来,也许它在某一天它会变成一笔财富了?不管怎么说,尝试记录工作的点滴都是一个不错的点子,呵呵。夸奖一下我自己! 在用modelsim 6.0 se作仿真的时候碰到一个错误,在xilinx的数据库里面发现原因如下: Problem Description: Keywords: ModelSim, MXE, MTI, error, VSIM ..

[查看全文]

FPGA有限状态机模拟I2C总线设计

2012-06-02

潘小冬

18

摘要:以I2C总线协议为根据。用有限状态机(FSM:Finite State Machine)设计了基于FPGA的I2C初始化程序模块。主要内容包括简述I2C总线的特点;介绍用FPGA中FSM开发I2C总线模块时的设计思想和实现过程;给出并解释了部分用Verilog HDL描述I2C总线初始化SAA7111和SAA7121的程序,最后在QuartusII中进行了I2C总线主从模 ..

[查看全文]

ModelSim SE仿真Altera库的建立

2012-06-02

shemily

25

(注:最近自己准备做后仿真,到坛子里看看了,发现一开始建库就是一个很大的问题。为了便以自己学习也为了给大家省点事,我花了十来个小时整理了一些资料,全部资料来自edacn.net/bbs的ModelSim的〈库〉,在下面的资料中不能一一列出作者,请各位网友多多包涵。下面的资料是大家的成果。by CHY 07.04.05) 1. modelsim怎 ..

[查看全文]

一个简单的总线轮询仲裁器Verilog代码

2012-06-02

17

下面这个是以输入信号作为状态机的转移条件,写得比较冗余: // // Verilog Module demo1_lib.bus_arbitor.arch_name // // Created: //by - Newhand //in - Shanghai ZhangJiang //at - 20:39:41 2003-12-03 // using Mentor Graphics HDL Designer(TM) // ///////////////////////////////////////////////////////// ..

[查看全文]

VHDL设计举例:步进电机控制器

2012-06-02

24

LIBRARY IEEE; USE IEEE.std_logic_1164.ALL; USE IEEE.std_logic_unsigned.ALL; USE IEEE.std_logic_arith.ALL; ENTITY step_motor IS PORT( f, p, d: INSTD_LOGIC:='0'; speed : inSTD_LOGIC_VECTOR(1 downto 0); coil : OUTSTD_LOGIC_VECTOR(3 downto 0) ); END step_motor; ARCHITECTURE behavior OF s ..

[查看全文]

S3C2410上Jffs2的移植

2012-06-02

赵印伟

17

参照llg写的关于hharm(e28f128flash)上的jffs2的移植 具体如下: 1.移植环境: CPU:ARMS3C2410 Linux version:2.4.18 Flash:Intel E28F128 2.修改设备号 由于ROM设备和MTDBlock设备的主设备号(major)都是31,所以如果你不想把JFFS2作为根文件系统的话,必须修改他们之一的major。如果你要修改JFFS2的设备ma ..

[查看全文]

实现USB2.0高速数据传输的问题探讨

2012-06-02

11

摘要:针对USB2.0高速数据传输在实际应用中存在的具体问题,深入分析了诸如协议开销、带宽分配、工作环境、主机硬件结构和操作系统配置、设备驱动程序等影响速度提高的种种因素。同时重点阐述了USB2.0设备接口中端点FIFO通道和GPIF通用可编程接口的关键作用。并利用USB2.0控制芯片EZ-USB FX2进行了不同模式下数据传输 ..

[查看全文]

C51指针类型和存储区的关系详解

2012-06-02

25

一、存储类型与存储区关系data--->可寻址片内ram bdata--->可位寻址的片内ram idata--->可寻址片内ram,允许访问全部内部ram pdata--->分页寻址片外ram (MOVX @R0) (256 BYTE/页) xdata--->可寻址片外ram (64k 地址范围) code--->程序存储区 (64k 地址范围),对应MOVC @DPTR二、指针类型和存储 ..

[查看全文]

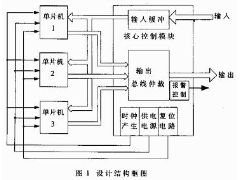

单片机多机冗余设计及控制模块的VHDL语言描述

2012-06-02

刘先昆 潘红兵

13

摘要:以三个单片机组成的系统为例介绍一种单片机多机冗余容错设计。阐述设计中关键的时钟同步技术和总线仲裁方法,给出控制模块的VHDL语言描述。 本文提出一种表决式单片机多机冗余设计方案。该方案不同于中央系统的多机冗余设计。大规模系统冗余大多采用完善而复杂的机间通讯协议实现系统重构,不太注重系统的实时性。本方 ..

[查看全文]

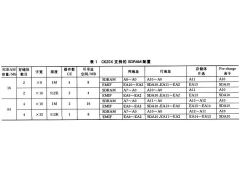

DSP片外高速海量SDRAM存储系统设计

2012-06-02

16

摘要:介绍使用同步动态RAM(SDRAM)扩展嵌入式DSP系统高速超大容量外部存储空间的设计方法;结合已成功实现的、基于TMS320C6201的数字信号处理系统,论述使用IS42S16400 SDRAM芯片设计DSP片外同步存储系统的具体实现方案;详细讨论TMS320c6201的EMI与SDRAM的接口设计及编程方法。在数字图像处理、航空航天等 ..

[查看全文]

51单片机 Keil C 延时程序的简单研究

2012-06-02

12

发信站: BBS 水木清华站 (Fri Apr 15 10:54:23 2005), 站内ft2 (to2too) 于(Mon Apr4 23:20:41 2005)提到:by: InfiniteSpace Studio/isjfk, 1.21.2004任何人都可以在注明原作者和出处的前提下随意转载这篇文章,但不得用于商业目的。应用单片机的时候,经常会遇到需要短时间延时的情况。需要的延时时间很短,一般都是几 ..

[查看全文]

推荐文章

-

热敏电阻温度阻值查询程序2024年11月13日 109

-

C99语法规则2024年11月16日 1011

-

FreeRTOS 动态内存管理2024年11月12日 484

-

一款常用buffer程序2024年11月06日 121

-

1602液晶显示模块的应用2012年08月03日 203

-

GNU C 9条扩展语法2024年11月18日 300

最新文章

-

Corext-M3中断的具体行为2025年11月11日 66

-

优秀的字符串哈希算法-ELFhash2024年11月26日 110

-

SD卡TF卡引脚定义2024年11月26日 105

-

C语言string.h常用函数重点说明2024年11月22日 62

-

C语言下划线命名法2024年11月22日 74

-

C数组 结构体 联合体快速初始化2024年11月22日 60

热门文章

-

C99语法规则2024年11月16日 1011

-

51单片机LED16*16点阵滚动显示2012年09月05日 672

-

FreeRTOS 动态内存管理2024年11月12日 484

-

ARM9远程图像无线监控系统2012年07月03日 435

-

用单片机模拟2272软件解码2012年09月06日 311

-

如何实现STM32F407单片机的ADC转换2024年11月15日 310