VHDL设计举例:一个游戏程序

2012-10-17

13

--Copyright (c) 1993,1994 by Exemplar Logic, Inc.All Rights Reserved. -- -- This source file may be used and distributed without restriction -- provided that this copyright statement is not removed from the file -- and that any derivative work contains this copyright notice. -- ----------- -- --This is a syn ..

[查看全文]

CPLD 120MHz高速A/D采集设计

2012-10-16

徐法东 翟正军

79

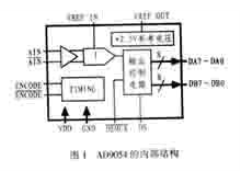

摘要:介绍了一种基于复杂可编程逻辑器件(CPLD)的120MHz高速A/D采集卡的设计方法。给出了这种采集卡的硬件原理电路和主要的软件设计思路。采用该设计方法设计的数据采集卡具有包括负延迟触发等多种触发方式,具有体积小,工作可靠,控制简单等特点。 关键词:高速A/D;CPLD;负延迟触发;EPM7128;AD9054 高速A/ ..

[查看全文]

用Verilog HDL实现I2C总线功能

2012-10-16

13

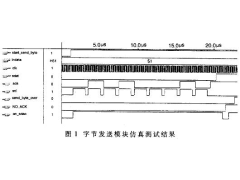

摘要: 简述了I2C总线的特点;介绍了开发FPGA时I2C总线模块的设计思想;给出并解释了用Verilog HDL实现部分I2C总线功能的程序,以及I2C总线主从模式下的仿真时序图。 关键词: I2C总线 FPGA Verilog HDL 时序 开发FPGA时,利用EDA工具设计芯片实现系统功能已经成为支撑电子设计的通用平台,并逐步向支持系统级的设计方向发 ..

[查看全文]

QT/E和Qtopia的编译经历

2012-10-16

15

(一)编译PC上的qpe 今天我给大家分享一下我自己从编译PC上的QT到编译ARM上的QT(交叉编译QPE)的过程,虽然QT不是自己的全部,但是毕竟在这半个月的环境搭建实验时间里,受到无数的打击,无所的失败,在QT中文网内朋友的鼓舞下,也慢慢成长起来,最后才搭建完成,所以我们开始吧! 首先说说编译PC上的QT/E,我起初的 ..

[查看全文]

触摸屏芯片ADS7846/ADS7843驱动程序(C51)

2012-10-16

21

/* [文件名] Touch.c [功 能] 8051单片机驱动ADS7846/ADS7843芯片 [简 介] ADS7846/7843芯片 适合用在4线制触摸屏,它通过标准SPI协议和CPU通信,操作简单,精度高,当触摸屏被按下时(即有触摸事件发生)则ADS7846向CPU发中断请求,CPU接到请求后,应延时一下再响应其请求,目的是为了消除抖动使得采样更准确。如果 ..

[查看全文]

基于PIC16F873的16路抢答器

2012-10-16

14

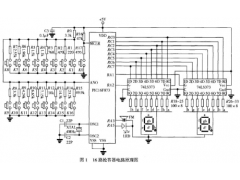

1 系统硬件设计美国Microchip Technology公司推出的PIC16F87X中档系列单片机,片内含有A/D、PWM、EEPROM等丰富的接口模块和FLASH程序存储器。借助于PIC16F873片内的ADC模块,使用一条I/O引脚,可以实现多个按钮开关的数字量输入问题。以此原理制成的16路抢答器,电路设计有抢答按钮开关、状态指示灯、复位开关、 ..

[查看全文]

FIR数字滤波器分布式算法的原理及FPGA实现

2012-10-16

9

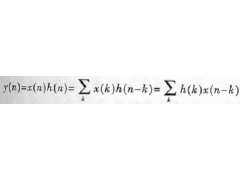

摘要: 在利用FPGA实现数字信号处理方面,分布式算法发挥着关键作用,与传统的乘积-积结构相比,具有并行处理的高效性特点。详细研究了基于FPGA、采用分布式算法实现FIR数字滤波器的原理和方法,并通过Xilinx ISE在Modelsim下进行了仿真。 关键词: 分布式算法 DALUT FPGA FIR 数字滤波器正在迅速地代替传统的由R、L、C元件 ..

[查看全文]

Keil C51 总线外设操作问题的深入分析

2012-10-16

9

阅读了《单片机与嵌入式系统应用》2005年第10期杂志《经验交流》栏目的一篇文章《Keil C5l对同一端口的连续读取方法》(原文)后,笔者认为该文并未就此问题进行深入准确的分析。文章中提到的两种解决方法并不直接和简单。笔者认为这并非是 Keil C51中不能处理对一个端口进行连续读写的问题,而是对Keil C51的使用不够熟悉和设 ..

[查看全文]

Arm结构体gcc内存边界对齐问题

2012-10-16

12

这段时间移植公司的linux i386程序到Arm linux平台,本以为是件工作量很小的事情,以为只要改几个驱动程序就OK了,没想到在应用程序这一块卡了很长时间。其中最烦的事情就莫过于结构体内存边界对齐了。搞了这么久,终于终结了一些小经验。 默认情况下,在32位cpu里,gcc对于结构体的对齐方式是按照四个字节来对齐的。看以下结 ..

[查看全文]

FPGA三国志-第三篇/SOPC篇

2012-10-15

wisdomz

21

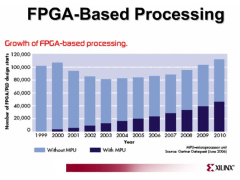

PLD的重新定义PLD是什么,Programmable Logic Device. 当然今天应该换个称呼了:Processor+ Logic+DSP 了,世界就是这样不停的变化来维持他的稳定。 表1列出了Altera®可编程解决方案的主要历史创新发展过程。,可以看到在2000年的时候,FPGA的厂商已经开始在嵌入式微处理器方面开始崭露头脚。 当然起初引来的也有一 ..

[查看全文]

基于Nios II的JPEG图像显示系统研究

2012-10-15

郭晓河

21

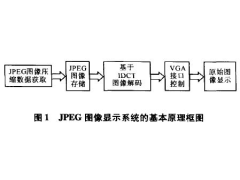

随着多媒体通信技术的发展,人们不再满足单一文字或声音的传递,从普通电话到视频电话,从SMS(short messaging service)到EMS(enhanced message service)再到MMS(multimedia messaging service),多媒体技术逐渐进入千家万户。因此,研究如何高效地处理多媒体信源,让其更方便有效地存储和传输是非常必要的。JPEG标 ..

[查看全文]

用CPU配置FPGA (四) 应用实例

2012-10-15

8

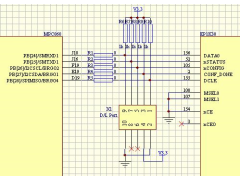

我们已在某单板上实现了该设计。现以该单板为例,说明如何实现CPU对FPGA的配置。 在该单板上是使用MPC860作CPU,BootROM采用SST39VF040,一片FPGA型号EP1K30QC208-3。我们在MCP860的PB口选5根线与EP1K30连接成PS配置方式,硬件连接参考第二章,Data0也由MPC860输出,信号定义见下表 MPC860引脚 I/O 信号 ..

[查看全文]

推荐文章

-

热敏电阻温度阻值查询程序2024年11月13日 109

-

C99语法规则2024年11月16日 1011

-

FreeRTOS 动态内存管理2024年11月12日 484

-

一款常用buffer程序2024年11月06日 121

-

1602液晶显示模块的应用2012年08月03日 203

-

GNU C 9条扩展语法2024年11月18日 300

最新文章

-

Corext-M3中断的具体行为2025年11月11日 66

-

优秀的字符串哈希算法-ELFhash2024年11月26日 110

-

SD卡TF卡引脚定义2024年11月26日 105

-

C语言string.h常用函数重点说明2024年11月22日 62

-

C语言下划线命名法2024年11月22日 74

-

C数组 结构体 联合体快速初始化2024年11月22日 60

热门文章

-

C99语法规则2024年11月16日 1011

-

51单片机LED16*16点阵滚动显示2012年09月05日 672

-

FreeRTOS 动态内存管理2024年11月12日 484

-

ARM9远程图像无线监控系统2012年07月03日 435

-

用单片机模拟2272软件解码2012年09月06日 311

-

如何实现STM32F407单片机的ADC转换2024年11月15日 310