用Verilog-HDL做CPLD设计(组合逻辑电路的实现)

2012-06-02

李媛媛 常晓明

13

Verilog-HDL与CPLD/FPGA设计应用讲座 第 7 讲 用Verilog-HDL做CPLD设计 组合逻辑电路的实现 7.1 与非门的实现 7.2 2-1数据选择器的实现 7.3 2位二进制编码器的实现 7.4 1位数据比较器的实现 本讲中,我们通过由浅入深的实例来介绍组合逻辑电路在目标板上是如何实现的。 7.1 与非门的实现 首先,来实现一个用两个开关控制一个灯的 ..

[查看全文]

Verilog HDL设计练习进阶(二)

2012-06-02

12

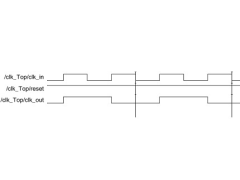

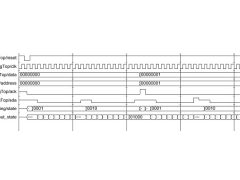

练习二. 简单时序逻辑电路的设计 目的:掌握基本时序逻辑电路的实现。 在Verilog HDL中,相对于组合逻辑电路,时序逻辑电路也有规定的表述方式。在可综合的Verilog HDL模型,我们通常使用always块和 @(posedge clk)或 @(negedge clk)的结构来表述时序逻辑。下面是一个1/2分频器的可综合模型。 // half_clk.v: module half_clk( ..

[查看全文]

Verilog Pli的基本使用方法(modelsim)

2012-06-02

18

内容未做证实,仅供参考。 1.hello.c文件内容 #include #include "veriuser.h" static PLI_INT32 hello() { printf("Hi there\n"); return 0; } s_tfcell veriusertfs[] = { {usertask, 0, 0, 0, hello, 0, "$hello"}, {0} /* last entry must be 0 */ }; 2.hello.v文件内容 module hello; initial begin $hello ..

[查看全文]

一个简单的总线轮询仲裁器Verilog代码

2012-06-02

18

下面这个是以输入信号作为状态机的转移条件,写得比较冗余: // // Verilog Module demo1_lib.bus_arbitor.arch_name // // Created: //by - Newhand //in - Shanghai ZhangJiang //at - 20:39:41 2003-12-03 // using Mentor Graphics HDL Designer(TM) // ///////////////////////////////////////////////////////// ..

[查看全文]

浅谈VHDL/Verilog的可综合性以及对初学者的一些建议

2012-06-02

16

一、HDL不是硬件设计语言 过去笔者曾碰到过不少VHDL或Verilog HDL的初学者问一些相似的问题,诸如如何实现除法、开根号,如何写循环语句等等。在这个论坛上,也时常能看到一些网友提出这一类的问题。 对于这些问题,首先要明确的是VHDL和Veriglog并非是针对硬件设计而开发的语言,只不过目前被我们用来设计硬件。HDL是Har ..

[查看全文]

Verilog HDL设计练习进阶(九)

2012-06-02

10

练习九.利用状态机的嵌套实现层次结构化设计 目的:1.运用主状态机与子状态机产生层次化的逻辑设计; 2.在结构化设计中灵活使用任务(task)结构。 在上一节,我们学习了如何使用状态机的实例。实际上,单个有限状态机控制整个逻辑电路的运转在实际设计中是不多见,往往是状态机套用状态机,从而形成树状的控制核心。这一点 ..

[查看全文]

推荐文章

最新文章

热门文章