静态时序分析在高速FPGA设计中的应用

2012-06-02

周海斌

28

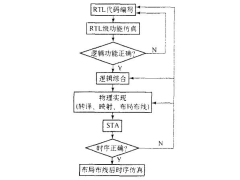

摘要:介绍了采用STA (静态时序分析)对FPGA (现场可编程门阵列)设计进行时序验证的基本原理,并介绍了几种与STA相关联的时序约束。针对时序不满足的情况,提出了几种常用的促进时序收敛的方法。结合设计实例,阐明了STA在高速、大规模FPGA开发中的应用。实践表明,随着数字设计复杂度的增加,在后端的时序验证环节,与传统的动 ..

[查看全文]

在Matlab中实现FPGA硬件设计

2012-06-02

江 霞

38

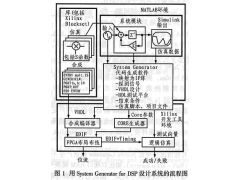

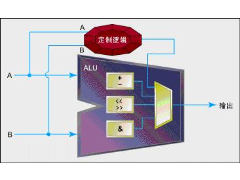

摘要 :System Generator for DSP是Xilinx公司开发的基于Matlab的DSP开发工具?熗?时也是一个基于FPGA的信号处理建模和设计工具。文章介绍了在Matlab中使用System Generator for DSP实现FPGA硬件设计的方法,同时给出了一个应用实例。 关键词 :Matlab;FPGA;System Generator;DSP 近年来,在数字通信、网络、视 ..

[查看全文]

基于FPGA的多路脉冲重复频率跟踪器

2012-06-02

12

摘要:在反辐射导弹的雷达导引头中,信号跟踪器的实时性是影响系统性能的重要因素之一。介绍了利用高性能FPGA丰富的资源实现的多路脉冲重复频率跟踪器,它解决了在密集信号环境下信号跟踪的实时性问题,减小了系统体积。经过实验验证,其各项指标均达到了设计要求。 随着高科技的迅速发展,现代战争已经不仅是传统意义战场上 ..

[查看全文]

FPGA直接数字频率合成器的设计

2012-06-02

周俊峰 陈 涛

9

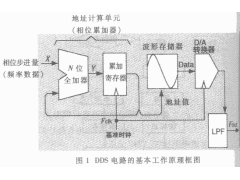

摘要:介绍了利用Altera的FPGA器件(ACEX EP1K50)实现直接数字频率合成器的工作原理、设计思想、电路结构和改进优化方法。 关键词:直接数字频率合成(DDS) 现场可编程门阵列(FPGA) 直接数字频率合成(Direct Digital Fraquency Synthesis,即DDFS,一般简称DDS)是从相位概念出发直接合成所需要波形的一种新的频率 ..

[查看全文]

Xilinx FPGA开发环境的配置

2012-06-02

风子心

24

一、配置Modelsim ISE的Xilinx的仿真库 1、编译仿真库: A、先将Modelsim安装目录C=Modeltech_6.2b下面的modelsim.ini改成存档格式(取消只读模式); B、在DOS环境中,进入Xilinx的根目录,然后依次进入bin,nt目录; C、运行compxlib -s mti_se -f all -l all -o C:Modeltech_6.2bxilinx_libs。 注意:需要根据你安装的modelsim目录 ..

[查看全文]

复用器重构降低FPGA成本

2012-06-02

13

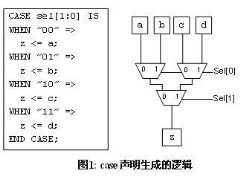

摘要 本文介绍了一种新的能够降低FPGA实际设计20%成本的综合算法。该算法通过减少复用器所需查找表(LUT)的数量来实现。算法以效率更高的4:1复用器替代2:1复用器树。算法性能关键在于寻找总线上出现的复用器数量。新的优化方法占用一定的逻辑,这些逻辑由总线进行分担,从而减少了总线上每个比特位所需的逻辑。 1.引言 复 ..

[查看全文]

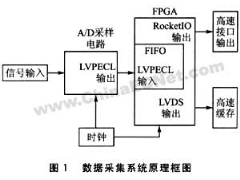

基于FPGA的高速数据采集系统接口设计

2012-06-02

黄伟,罗新民

16

当前,越来越多的通信系统工作在很宽的频带上,对于保密和抗干扰有很高要求的某些无线通信更是如此,随着信号处理器件的处理速度越来越快,数据采样的速率也变得越来越高,在某些电子信息领域,要求处理的频带要尽可能的宽、动态范围要尽可能的大,以便得到更宽的频率搜索范围,获取更多的信息量。因此,通信系统对信号处理 ..

[查看全文]

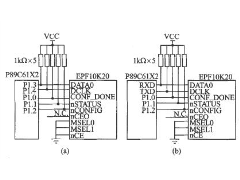

基于单片机P89C61X2的FPGA配置

2012-06-02

胡远望

10

大部分FPGA采用基于SRAM(静态随机存储器)的查找表逻辑形成结构,就是用SRAM构成逻辑函数发生器。SRAM工艺的芯片在掉电后信息就会丢失,需要外加一片专用配置芯片。在上电时,由这个专用配置芯片把数据加载到FPGA中,然后FPGA就可以正常工作。这就是在线可重配置ICR(In-Circuit Reconfigurability)方式。 Altera公 司生 ..

[查看全文]

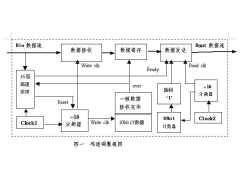

用FPGA实现非标码速向标准码速的调整

2012-06-02

33

摘要:本文主要讨论了如何利用FPGA可编程芯片实现计算机输出的异步非标码速(如9.6k、19.2k、57.6k、115.2k、460.8k等)到其邻近的标准码速(如64k、128k、256k、512k)的调整,实现该数据与通用传输系统的适配,以便能进行远程监控。 关键词:码速调整 FPGA 一、概述 现在,利用计算机进行异地数据采集正应用到越来越 ..

[查看全文]

使用基于FPGA的硬件方法实现算法加速

2012-06-02

Lara Simsic

14

当设计者试图从算法中获得最佳性能但软件方法已无计可施时,可以尝试通过硬件/软件重新划分来进行加速。FPGA易于实现软件模块和硬件模块的相互交换,且不必改变处理器或进行板级变动。本文阐述如何用FPGA来实现算法的硬件加速。 如果想从代码中获得最佳性能,方法包括优化算法、使用查找表而不是算法、将一切都转换为本地 ..

[查看全文]

如何搭建Xilinx FPGA开发环境

2012-06-02

风子心

6

一、计算机硬件环境要求 : 1、操作系统: Microsoft Windows XP Home Edition SP2 2、基本配置: A、处理器:Intel CPU T2050 1.6GHz B、内存:512MB C、硬盘:60GB(其中软件安装的空问需要3GB) 补充: 上面的配置为笔记本的配置。因此对显卡没有什么特殊的要求。有条件的话,尽可能选择更高的配置。这样软件跑起来会更快。 ..

[查看全文]

推荐文章

最新文章

热门文章